A-SSCC

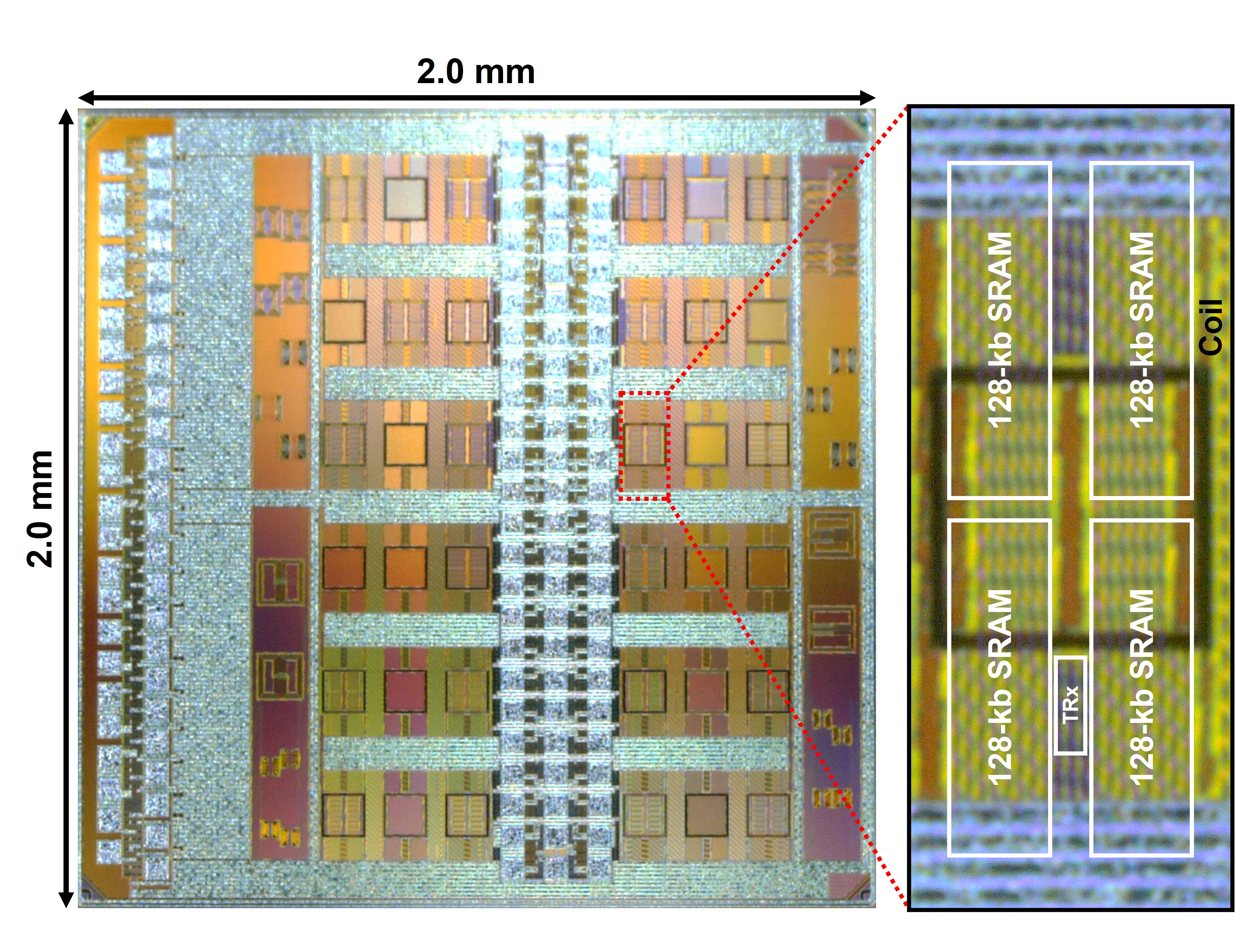

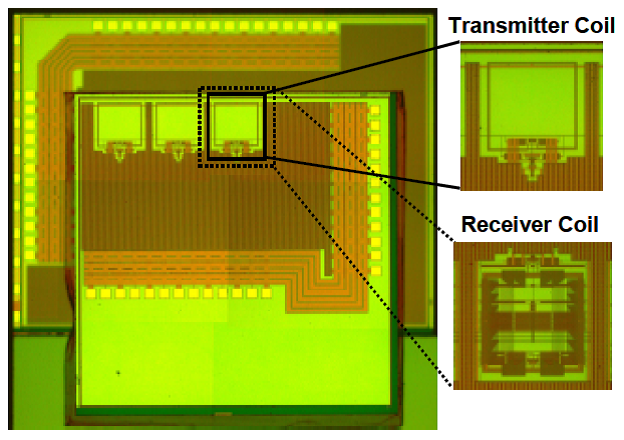

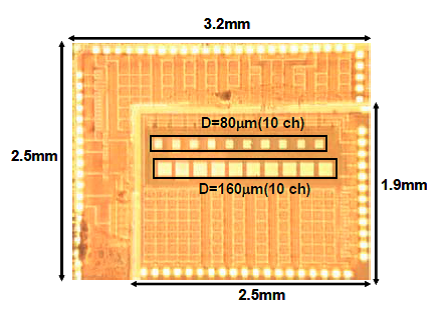

A 12.8-Gbps 0.5-pJ/b Encoding-less Inductive Coupling Interface Using Clocked Hysteresis Comparator for 3Dstacked SRAM in 7-nm FinFET

PDF 2022

12.8Gbps 0.5pJ/bの三次元積層SRAM向け誘導結合無線インタフェースを7nm FinFETプロセスで開発しました。SRAM直上に配置されたコイルとクロックトヒステリシスコンパレータを用いた同期式通信のおかげで、高い面積効率とエネルギー効率を達成しました。

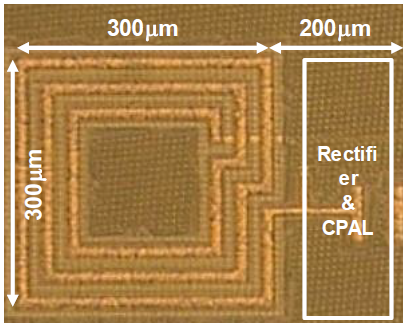

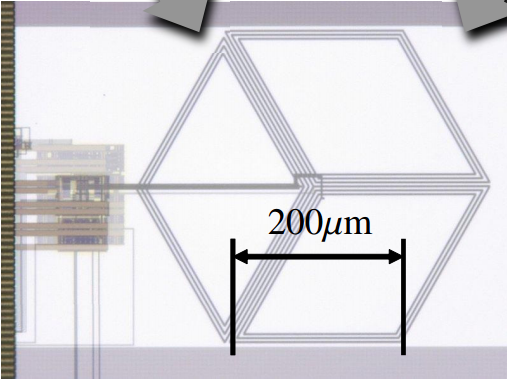

A 5-GHz 0.15-mm2 Collision Avoidable RFID Employing Complementary Pass-transistor Adiabatic Logic with an Inductively Connected External Antenna

PDF 2021

断熱的論理回路と磁界結合コイルを用いた衝突回避機能付きの小型パッシブRFIDタグを開発しました。IDが出力されるタイミングをずらすことでタグ同士の干渉を回避することができ、アンテナを磁界結合させることで接合費用を抑えることができます。

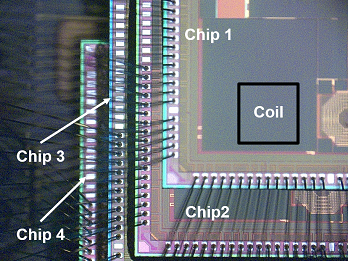

An Inductive-Coupling Bus with Collision Detection Scheme Using Magnetic Field Variation for 3-D Network-on-Chips

PDF 2016

3D-NoCsに向けて、マルチドロップバス方式誘導結合通信と、磁界変化を利用したバス上のデータ衝突検知手法を提案しました。従来方式と比較して1/3のコイル数、かつ低レイテンシでの通信が可能になります。

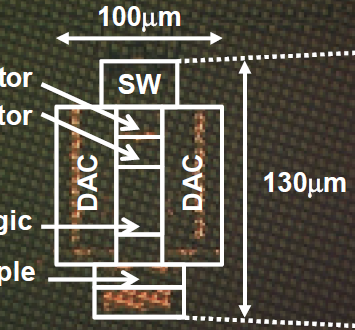

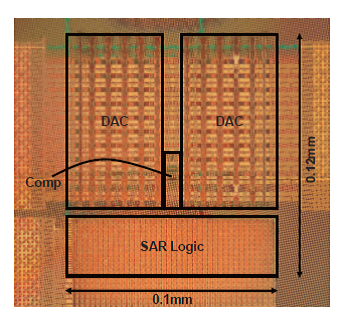

A 40nm CMOS Full Asynchronous Nano-Watt SAR ADC with 98% Leakage Power Reduction by Boosted Self Power Gating

PDF 2012

超低電圧、超低消費電力の逐次比較型ADCを開発しました。完全非同期で動作するとともに、昇圧型自己電源遮断技術をデジタル部分とアナログ部分の両方に用いることで、高い変換精度と、98%のリーク電力削減を達成しました。

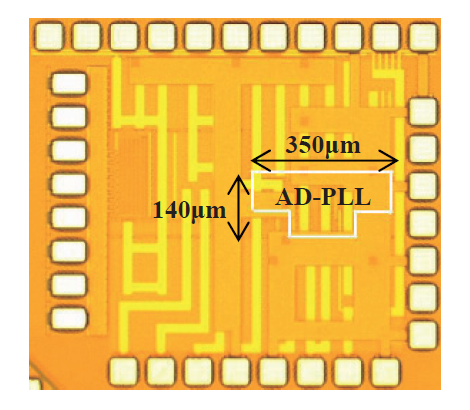

A 0.5V 10MHz-to-100MHz 0.47µW/MHz Power Scalable AD-PLL in 40nm CMOS

PDF 2012

超低電圧、低消費電力で動作するAD-PLLを開発しました。8相のDCOを繋げたTDCによって0.5Vで動作可能で、10MHzから100MHzの範囲内で0.47?W/MH以下の電力効率を実現しました。無線センサノード内のマイコンの、クロック生成に最適です。

Rotary Coding for Power Reduction and S/N Improvement in Inductive-Coupling Data Communication

PDF 2011

ロータリエンコーダ手法での誘導結合通信を開発しました。従来より消費電力は50%以下であり、ジッター耐性が高くなります。非接触メモリーカードインターフェース、3次元集積されたIC内の通信などに応用可能です。

1W 3.3V-to-16.3V Boosting Wireless Power Transfer Circuits with Vector Summing Power Controller

PDF 2011

大容量非接触メモリーカードへの小型無線給電システムを開発しました。コイルをトランスとして用いて給電と同時に昇圧することで、受電側の昇圧回路を排し、低コスト化と全体の伝送効率の改善が可能です。

A 0.6V Noise Rejectable All-Digital CDR with Free Running TDC for a Pulse-Based Inductive-Coupling Interface

PDF 2011

誘導結合パルス通信のための完全デジタルCDRを開発しました。パルス雑音の除去のためにTDCが用いられています。0.6Vで正常に動作し、12Gb/sでの消費電力は4.7pJ/sに抑えられています。

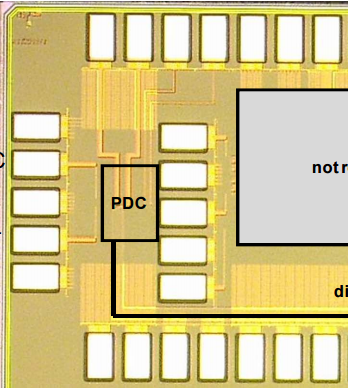

A Phase-to-Digital Converter for Wide Tuning Range and PVT Tolerant ADPLL Operating Down to 0.3V

PDF 2010

位相-デジタル変換器(PDC)を開発しました。従来の時間-デジタル変換器(TDC)における較正の手間を減らすことができ、広いチューニングレンジとPVTばらつきへの耐性を持つ低電圧ADPLLへの応用が期待されます。

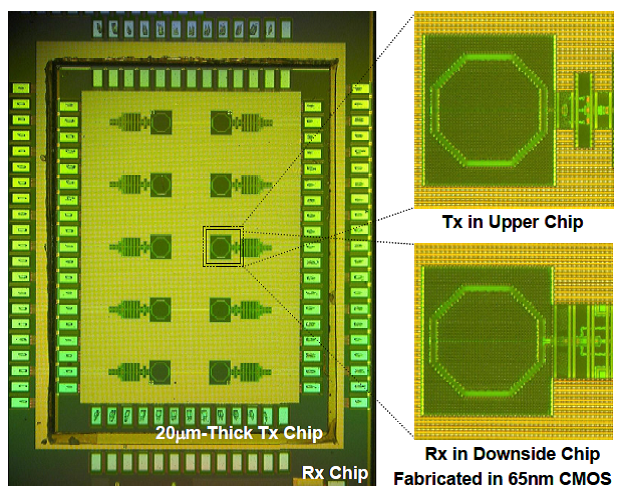

A 30Gb/s/link 2.2Tb/s/mm2 Inductively-Coupled Injection-Locking CDR

PDF 2010

DRAMインターフェース向けの、誘導結合を用いた高速注入同期型CDRを開発しました。XORを用いたエッジ検出器を排することで動作速度を向上させ、従来に比べ、2倍の面積効率を達成しました。

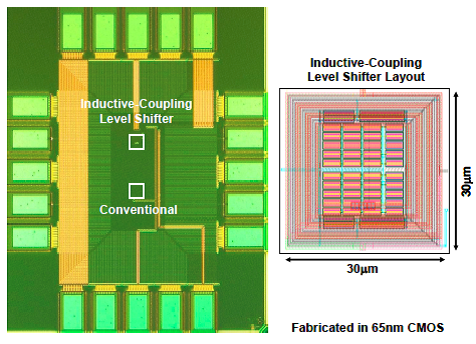

A 0.45V-to-2.7V Inductive-Coupling Level Shifter

PDF 2010

0.45Vから2.7Vに変換可能なレベルシフタを開発しました。コイルによる誘導結合を用いることで、広い動作範囲を確保しながら、従来に比べ、1/2のエネルギー効率、1/4の遅延時間を達成しました。

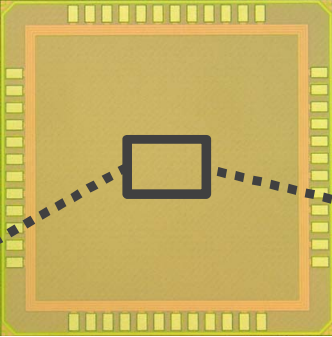

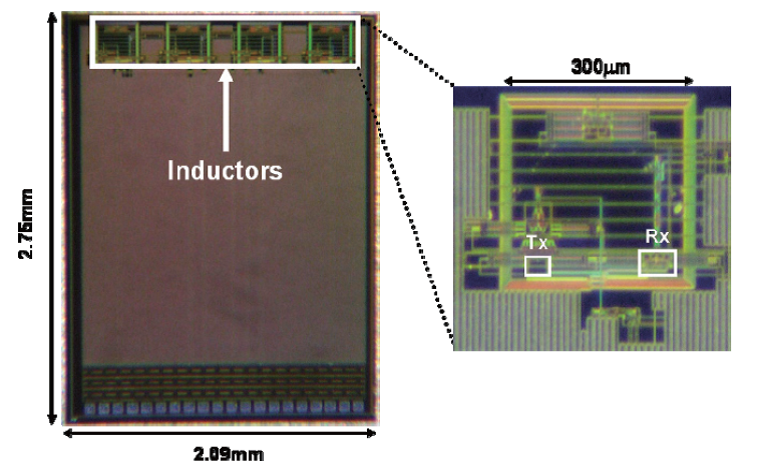

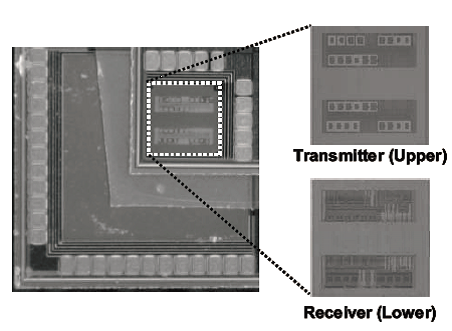

A Wafer Test Method of Inductive-Coupling Link

PDF 2009

誘導結合によるチップの3次元集積について、集積する前に、送信機および受信機の動作を確認するテスト法を提案しました。1チップ内の送信機と受信機間の通信試験によって、正常かどうかを確認します。

An Extended XY Coil for Noise Reduction in Inductive-Coupling Link

PDF 2009

コイルに入るノイズを低減するレイアウト手法として、グラウンドシールドを用いた拡張XYコイルを提案しました。ノイズ低減によってBERの改善が可能で、送信電力の削減に繋がります。

A 9b 100MS/s 1.46mW SAR ADC in 65nm CMOS

PDF 2009

9b、100MS/s、1.46mWの逐次比較型ADCを開発しました。3段階の電荷再分配技術によって、DACのスイッチング効率およびセットリングタイムを向上させ、39fJ/conversion-stepを達成しました。

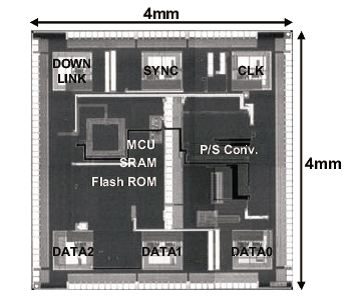

A Wireless Real-Time On-Chip Bus Trace System Using Quasi-Synchronous Parallel Inductive Coupling Transceivers

PDF 2008

ワイヤレスリアルタイムバストレースシステムを開発しました。準同期型の並列誘導結合通信を用いることで、高ノイズ耐性、低消費電力を維持しながら300psのタイミングマージンを達成できます。

A 65 fJ/b Inductive-Coupling Inter-Chip Transceiver Using Charge Recycling Technique for Power-Aware 3D System Integration

PDF 2008

チップ間誘導結合通信を用いた省電力3次元集積のための、送受信機を開発しました。交差型のデイジーチェーンによって電荷を再利用し、性能を損なうことなく消費電力を削減できます。

Interference from Power/Signal Lines and to SRAM Circuits in 65nm CMOS Inductive-Coupling Link

PDF 2007

電源、信号線の誘導結合通信への干渉、および誘導結合通信のSRAMへの干渉について解析しました。メッシュ状の電源線が特に影響が強く、またSRAMへの干渉は小さいことを示しました。

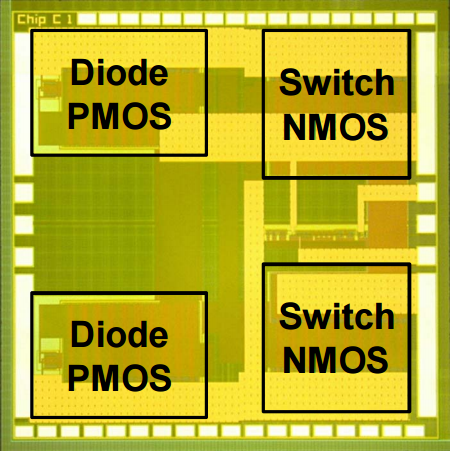

A 2Gb/s Bi-Directional Inter-Chip Data Transceiver with Differential Inductors for High Density Inductive Channel Array

PDF 2007

チップ間の高密度誘導結合通信のための、双方向送受信機を開発しました。差動のインダクタを用いることで、複雑な回路技術を用いることなく容易に通信が可能となり、従来に比べ、2倍のチャネル面積効率を達成しました。

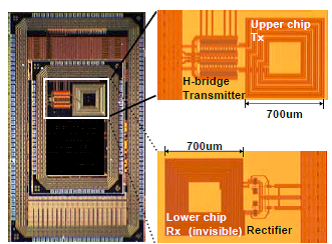

Non-Contact 10% Efficient 36mW Power Delivery Using On-Chip Inductor in 0.18-µm CMOS

PDF 2007

誘導結合を用いた、3次元集積されたチップ間の無線給電システムを提案、実装しました。新規のトポロジーの整流器と、最適化されたオンチップインダクタを用いることで、従来に比べ、13倍の受信電力を達成しました。