CICC

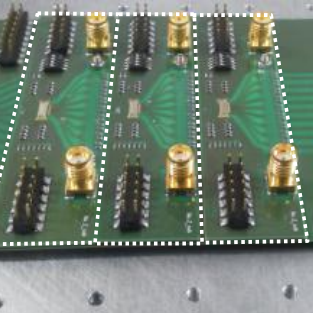

A 12.5Gb/s/Link Non-Contact Multi Drop Bus System with Impedance-Matched Transmission Line Couplers and Dicode Partial-Response Channel Transceivers

PDF 2012

TLCをマルチドロップバスの各信号分岐点に適用することで信号反射を抑制し、高速化を達成しました。信号符号化とメモリレスな送受信機を採用することで、従来より2.5倍の高速化と高信頼化を同時に達成しました。

A 100Mb/s 13.7pJ/bit DC-960MHz Band Plesiochronous IR-UWB Receiver with Costas-Loop Based Synchronization Scheme in 65nm CMOS

PDF 2012

コスタスループによる同期方式を用いた、DC-960MHz帯のインパルス無線用超広帯域受信機を開発しました。従来のようにADCやベースバンドデジタル信号処理の必要がなく、100Mb/s、13.7pj/bitでの動作を達成しました。

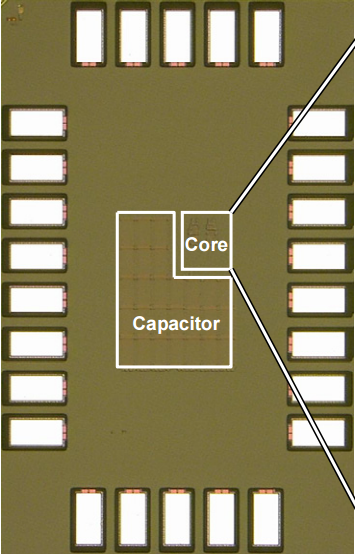

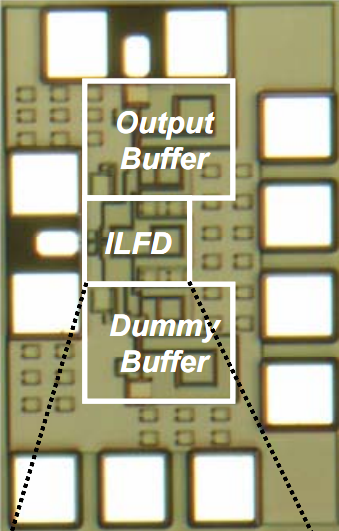

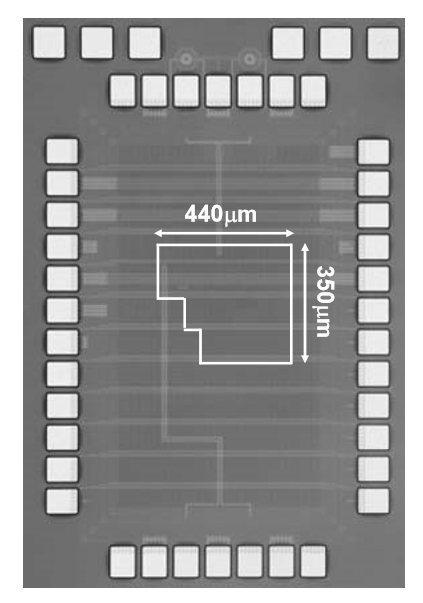

A 60-GHz 1.65mW 25.9% Locking Range Multi-Order LC Oscillator Based Injection Locked Frequency Divider in 65nm CMOS

PDF 2010

電源電圧1.2V、消費電力1.65mWの、60GHz帯注入同期型分周器(ILFD)を開発しました。複数次のLCフィルタを持つLC発振器を用いることで、48.5-62.9GHz(25.9%)の広いロックレンジを達成しました。

A 6Gb/s Receiver With Discrete-Time Based Channel Filtering For Wireline FDM Communications

PDF 2010

有線FDM相互通信に向けた6Gb/s受信機を開発しました。S/H回路と差動電流加算器を用いたフィルタリング技術と、同位相振幅のみに着目するクロック回復技術により、FDM信号の高速な復調と同期が可能となりました。

47% Power Reduction and 91% Area Reduction in Inductive-Coupling Programmable Bus for NAND Flash Memory Stacking

PDF 2009

SSDにおけるNANDフラッシュメモリアクセスのためのプログラミング可能な誘導結合母線を開発しました。従来に比べ伝送電力を47%、レイアウトにおけるコイルの面積を91%削減しました。

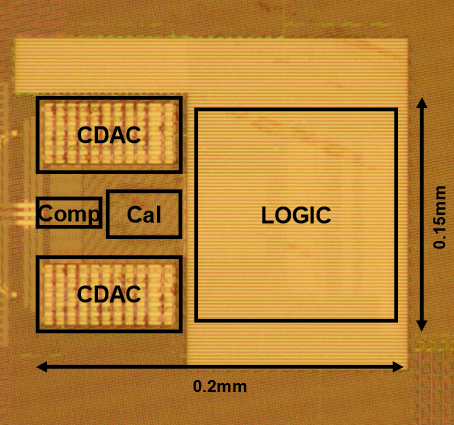

Split Capacitor DAC Mismatch Calibration in Successive Approximation ADC

PDF 2009

スプリットキャパシタDACの校正手法を提案しました。従来よりも大きなブリッジキャパシタを用いる事でミスマッチを埋めるチューニングを可能にしました。正確な校正のためにコンパレータのオフセットをキャンセルしています。

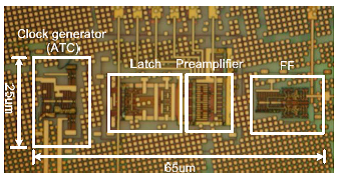

A Dynamic Offset Control Technique for Comparator Design in Scaled CMOS Technology

PDF 2008

コンパレータの電荷補償によるオフセット制御の原理を解析し、動的オフセット制御技術を提案しました。アナログ-時間変換器を用いた時間的制御による電荷補償によって、オフセットを制御します。

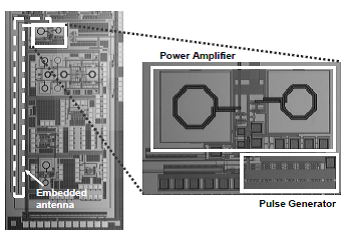

A 750Mb/s 12pJ/b 6-to-10GHz Digital UWB Transmitter

PDF 2007

6-10GHz帯を用いた、オールデジタルの超広帯域無線機を開発しました。2位相偏移変調された500psのパルスを用いて、750Mb/sの通信速度、12pJ/bのエネルギー効率を達成しました。低コスト近距離無線通信システムに応用可能です。

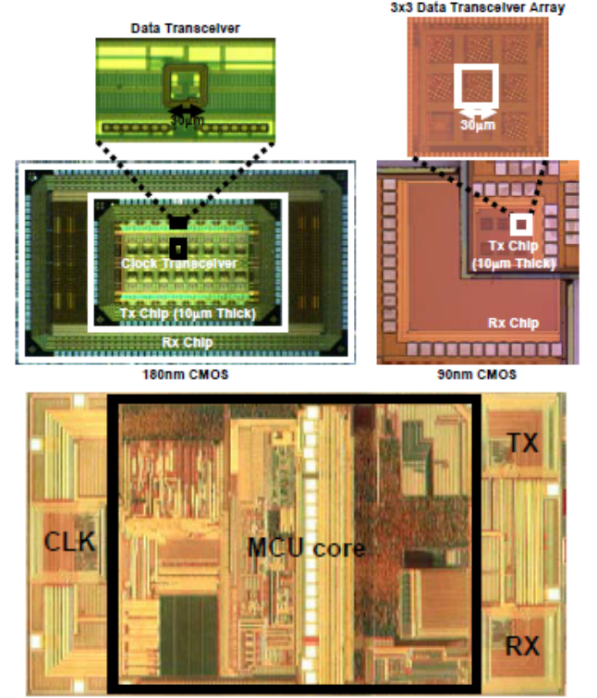

Wideband Inductive-coupling Interface for High-performance Portable System

PDF 2007

広帯域、低電力、低コストのパルス誘導結合インターフェースを用いて、SiP用チップ間通信において0.14pJ/bを達成し、また、LSIパッケージ内のチップモニタリング用の非接触インターフェースを開発しました。

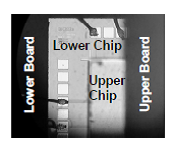

Chip-to-Chip Inductive Wireless Power Transmission System for SiP Applications

PDF 2006

誘導結合によるチップ間無線給電システムを開発し、その実現可能性について示しました。2.5mWの送信電力で、0.5VのDC出力電圧を達成しました。また、共振用のキャパシタ付加による改善法を提案しました。

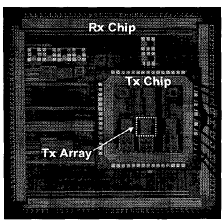

Cross Talk Countermeasures in Inductive Inter-chip Wireless Superconnect

PDF 2004

チップ間誘導結合通信について、チャネルをアレイ状に配置した際のクロストークについて解析、測定しました。また、クロストークへの対策について、最適な通信距離の設定と、TDMA方式による通信を提案しました。

Utilizing surplus timing for power reduction

PDF 2001

消費電力削減の手法として、複数の電源電圧、閾値電圧、トランジスタのサイズを用いる手法について、理論解析モデルを提案しました。また、将来的な設計について知見を示しました。

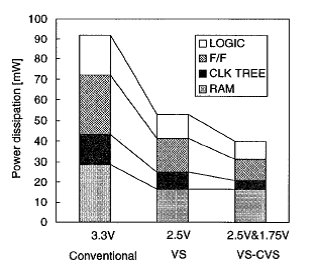

A top-down low power design technique using clustered voltage scaling with variable supply-voltage scheme

PDF 1998

電源電圧可変調整技術とクラスター化電圧スケーリングを用いた低電力回路のトップダウン設計法、およびレベルシフタとフリップフロップの機能を併せ持つ新規回路を提案しました。

A 300MIPS/W RISC Core Processor with Variable Supply-Voltage Scheme in Variable Threshold-Voltage CMOS

PDF 1997

閾値電圧可変調整技術を併用した、DC-DCコンバータを用いた電源電圧可変調整技術を提案しました。システムの性能要求に応じて電源電圧を調整し、動作速度と消費電力のトレードオフを取ることができます。

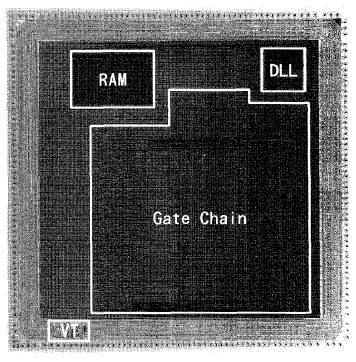

A High-speed Low-Power 0.3µm CMOS Gate Array with Variable Threshold Voltage (VT) Scheme

PDF 1996

基板バイアスを用いた閾値電圧可変調整技術を提案しました。システム待機時はトランジスタの閾値電圧を高くしてリークを減らし、動作時は閾値電圧を低くして低電源電圧で動作させることで、高速かつ低消費電力を実現できます。

A 51k-gate low power ECL gate array family with metal-compiled and embedded SRAM

PDF 1993

最大51kゲート密度の80ps、1mW/gateの直列ゲートECLゲートアレイファミリーが説明されています。このファミリーはTyp 2.5ns TTAを持つメタルコンパイルドSRAMと2.0ns TTAを持つエンベンデッドSRAMの双方をサポートしています。

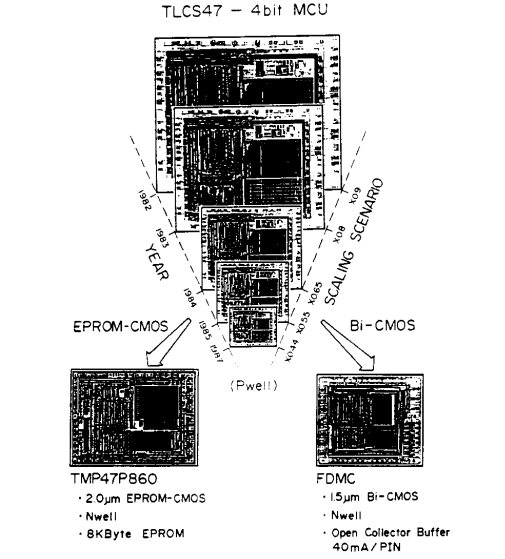

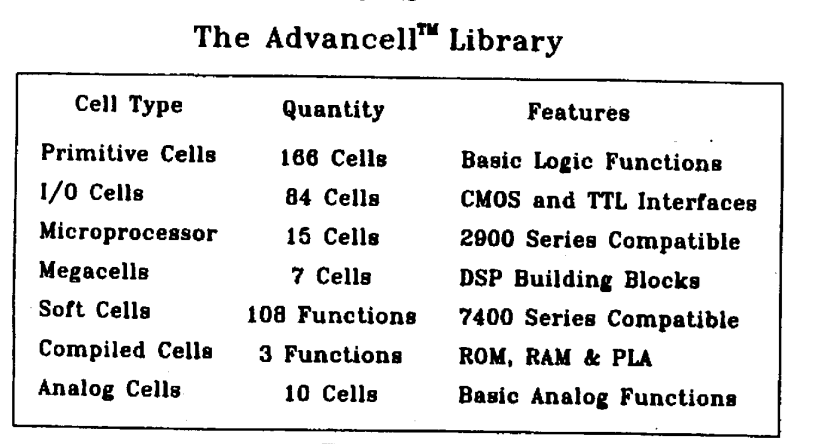

Unified_design_methodology_and_device_architecture_for_multi-generation_ASIC_applications

PDF 1988

ASICの要求に対する最も効率的なソリューションの1つとして統一された設計方法論とデバイスアーキテクチャについて説明します。オリジナルのデザインの生成に関係なく、様々なデザインをライブラリィとして蓄積して活用できるデザイン統一が確立されています。

A high perfomance scalable standard cell library with true second sourcing

PDF 1987

サブナノセコンドの負荷遅延を伴う1.5ミクロン2層メタルCMOS標準セルライブラリィが議論されています。ライブラリィには160以上のスタンダードセル、80のI/Oセルと17290のメガセルがあり、セコンドソースがあります。