ISSCC

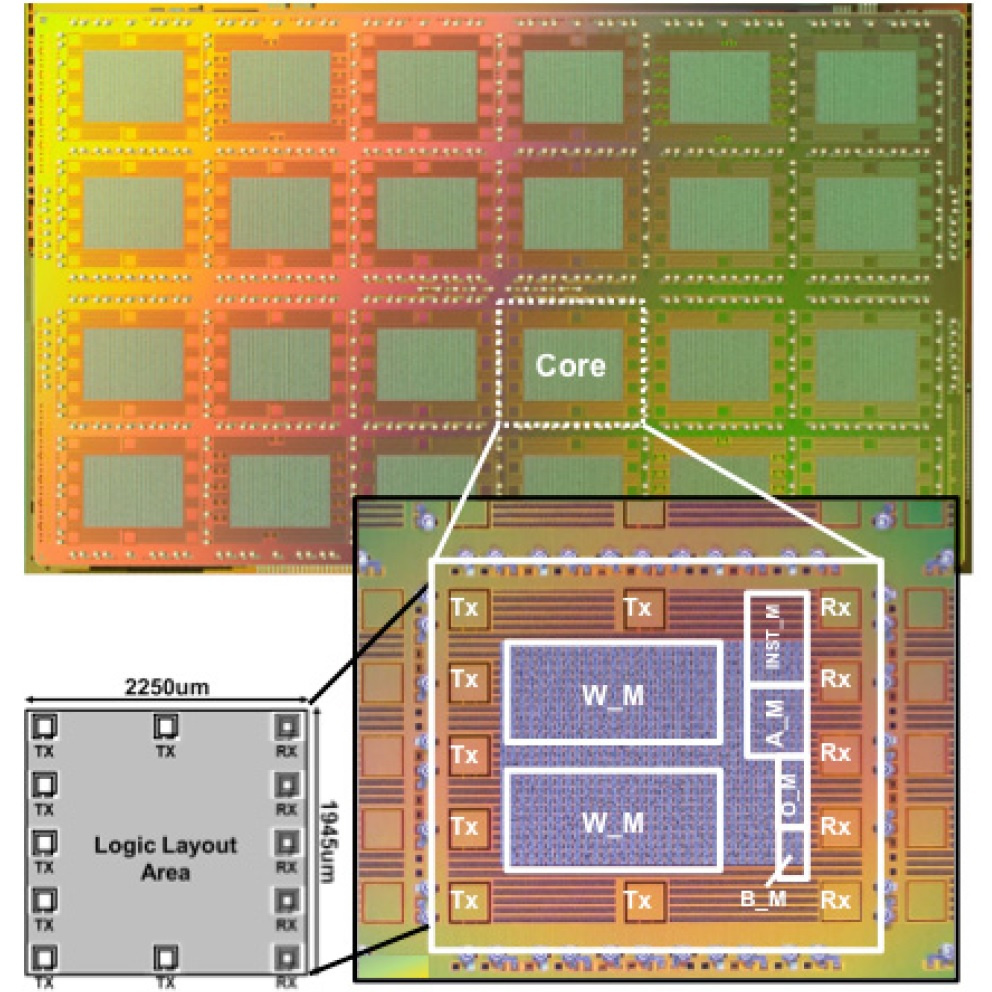

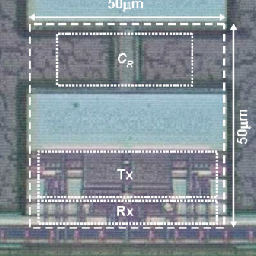

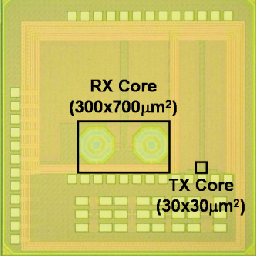

QUEST: A 7.49TOPS Multi-Purpose Log-Quantized DNN Inference Engine Stacked on 96MB 3D SRAM Using Inductive-Coupling Technology in 40nm CMOS

PDF 2018

対数量子化近似に基づくDNN推論アクセラレータを開発しました。アクセラレータとSRAMチップ8枚を積層し、磁界結合を利用して通信することで、大メモリ容量、低アクセス遅延、高バンド幅を実現しています。ピーク性能は7.49TOPSを達成しました。

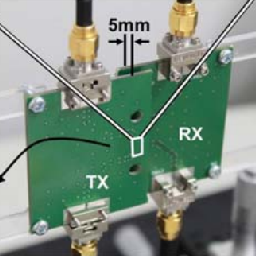

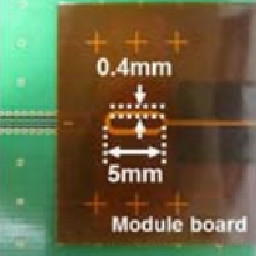

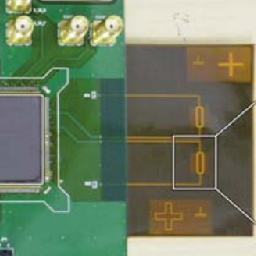

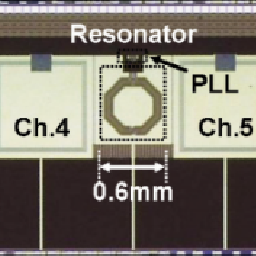

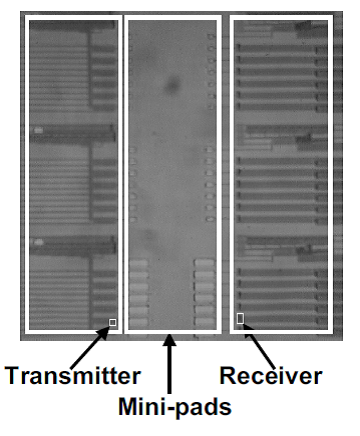

A 6Gb/s 6pJ/b 5mm-Distance Non-Contact Interface for Modular Smartphones Using Two-Fold Transmission Line Coupler and EMC-Qualified Pulse Transceiver

PDF 2015

モジュール型スマートフォン用途に小型・長距離の非接触コネクタ技術T-TLCを開発しました。従来の同接続距離のインタフェースと比較し、結合器面積を1/24、消費電力を1/6に 削減しました。EMC特性は実用上問題ありません。

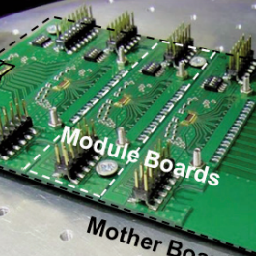

A 6.5Gb/s Shared Bus using Electromagnetic Connectors for Downsizing and Lightening Satellite Processor System by 60%

PDF 2015

衛星機器用途に振動耐性に優れる非接触バス技術を開発しました。ロケット打ち上げ時と同等の振動を印加しても、通信エラーは発生しません。通信を3倍高速化でき、固定治具 もないため、コネクタサイズを1/246に削減しました。

An Electromagnetic Clip Connector for InVehicle LAN to Reduce Wire Harness Weight by 30%

PDF 2014

車の電子制御化には電子機器を繋ぐ配線本数の削減と高速化が必要です。配線を被膜の上から挟むだけで従来比30%軽量・20倍高速な車載LANを構築できるクリップ型電磁界コネクタを開発しました。EMC 振動耐性に優れます。

A 6nW InductiveCoupling WakeUp Transceiver for Reducing Standby Power of NonContact Memory Card by 500×

PDF 2013

非接触メモリーカード向け無線制御回路を開発しました。トリガパルス生成回路、自動オフセット生成回路の導入により応答速度向上とスタンバイ消費電力削減を同時に達成、さらにブロック共有によりレイアウト面積の削減にも成功しました。

A 0.15mmThick NonContact Connector for MIPI Using Vertical Directional Coupler

PDF 2013

TLCをMIPIの規格に適合させ、LCDでの通信を可能にしました。1つのTLCにつき2つのデータを送れるようにし、TLC2つでMIPIの最大速度である6Gb/sを達成しました。また通信速度によらず一定の消費電力を実現し、様々な通信速度となるMIPIに適合します。

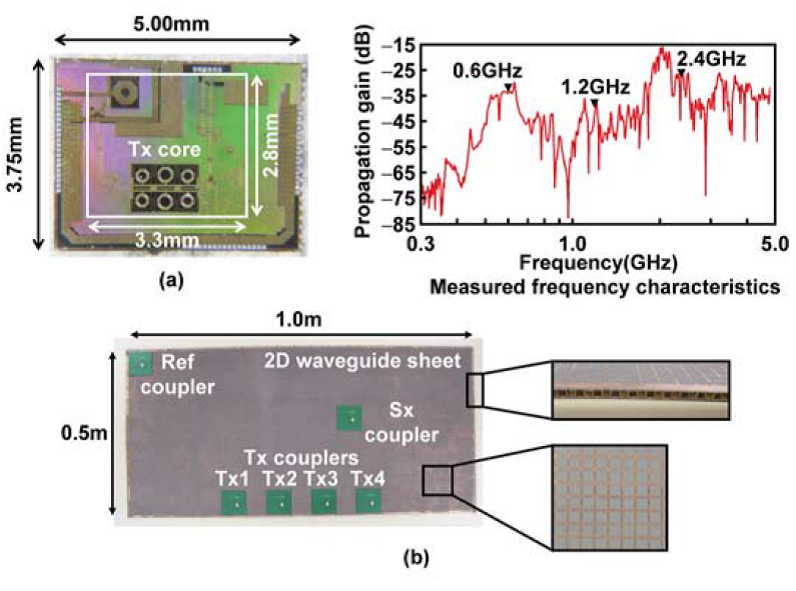

Retrodirective Transponder Array with Universal On-Sheet Reference for Wireless Mobile Sensor Networks Without Battery or Oscillator

PDF 2013

フレキシブルなバッテリーレスのセンサネットワーク実現のために、2次元導波シートを用いたトランスポンダを開発しました。位相シフトを用いたビームフォーミング技術により、高効率の電力伝送を実現します。

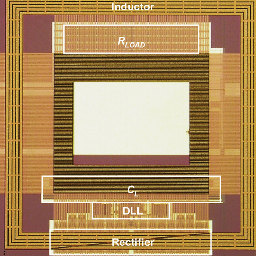

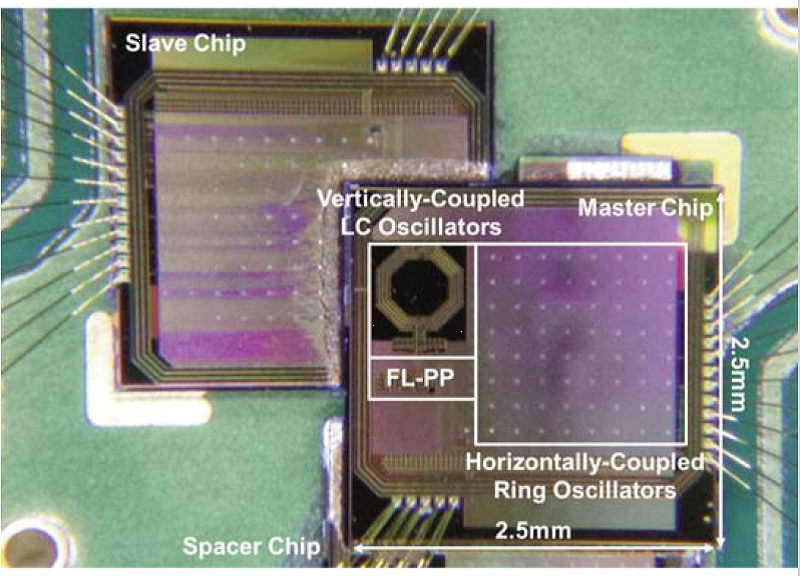

3D Clock Distribution Using Vertically/Horizontally-Coupled Resonators

PDF 2013

垂直/水平結合された共振器を用いた、3次元クロック分配技術を提案しました。垂直に結合されたLC共振器と、水平に結合されたリングオシレータによって、低スキュー、低ジッタ、低電力のクロック分配を実現しました。

A 7Gb/s/Link NonContact Memory Module for MultiDrop Bus System Using EnergyEquipartitioned Coupled Transmission Line

PDF 2012

TLCは反射のない信号分岐ができますが、マルチドロップにすると後段のTLCでエネルギーが不足します。そこで、各モジュールにエネルギーの等分配が可能なEE-TLCを開発しました。7Gb/sで5段の接続に成功し、メモリモジュールへの応用が可能です。

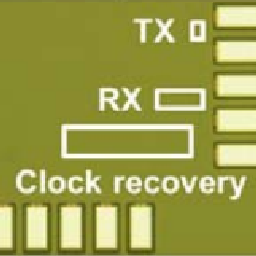

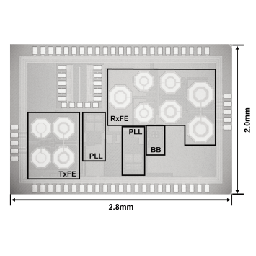

A 2Gb/s 150mW UWB DirectConversion Coherent Transceiver with IQSwitching Carrier Recovery Scheme

PDF 2012

IQスイッチングキャリアリカバリを用いた短距離通信向け送受信機を開発しました。RX側での動的なクロスポイント検索によりRXクロック位相の最適化を行い変調後信号振幅を大きくし、低電力・高速な動作が可能です。

A 12Gb/s NonContact Interface with Coupled Transmission Lines

PDF 2011

電磁界結合による非接触コネクタ(TLC)を開発しました。磁界結合に比べて広帯域で、インピーダンス整合が可能なために信号の反射を防ぐことができるため、高速な通信が可能です。通信距離1mmで12Gb/sの通信を実現しました。

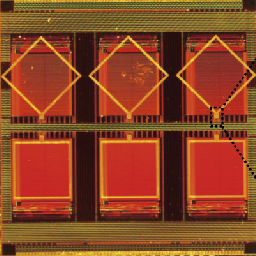

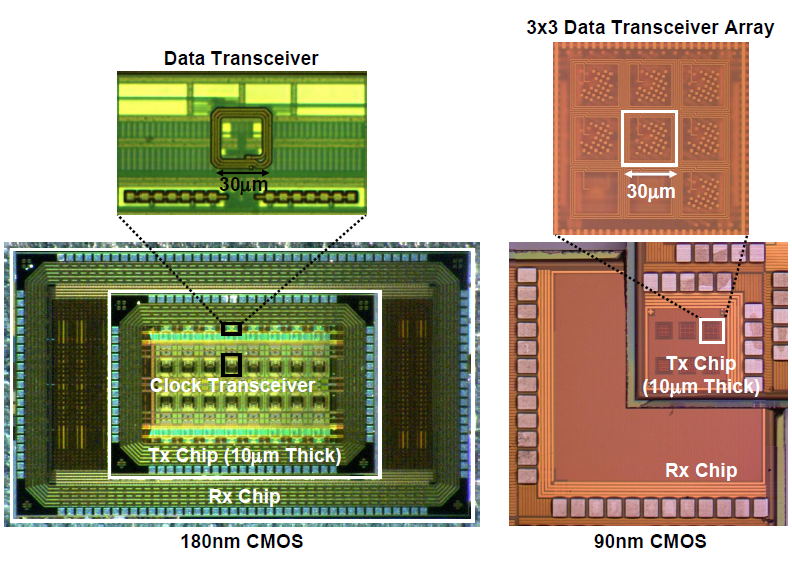

A 2.7Gb/s/mm2 0.9pJ/b/Chip 1Coil/Channel ThruChip Interface with Coupled- Resonator-Based CDR for NAND Flash Memory Stacking

PDF 2011

NANDフラッシュメモリ向け誘導結合インターフェースを開発しました。リレートランスミッション方式の導入及び結合共振器とCDRの利用によるクロックリンクの排除により単位面積あたりの帯域を10倍に向上し、消費電力も削減しました。

6W/25mm2 Inductive Power Transfer for Non-Contact Wafer-Level Testing

PDF 2011

ウェーハテストを非接触で行えるよう、磁界によって電力供給を行う手法を開発しました 。プローブを使わないことによって、low-k層へのダメージやパッドの変形を回避できます 。25mm2の面積で6Wの電力伝送が可能です。

A 2Gb/s 1.8pJ/b/chip Inductive-Coupling Through-Chip Bus for 128-Die NAND-Flash Memory Stacking

PDF 2010

TCIを用いた積層NANDフラッシュメモリにおいて、従来手法の33%の電力で通信を実現しました。チップを螺旋階段状に積層し、従来よりも高さを低くすることで、リピータの 数を減らし、低消費電力を実現しました。

A 2.5Gb/s/ch 4PAM Inductive-Coupling Transceiver for Non-Contact Memory Card

PDF 2010

FCB上に作成したコイルを用いてメモリーカードの非接触通信を実現しました。4PAMに よる通信を可能にすることで2.5Gb/s/chで高速動作し 送信電力の自動調節によって通信 距離が0.5~1mmの間で変化しても通信が可能です。

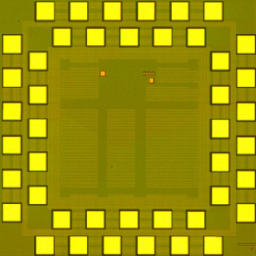

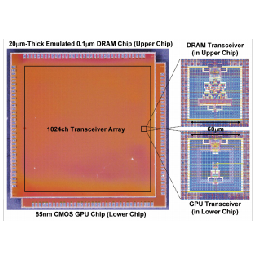

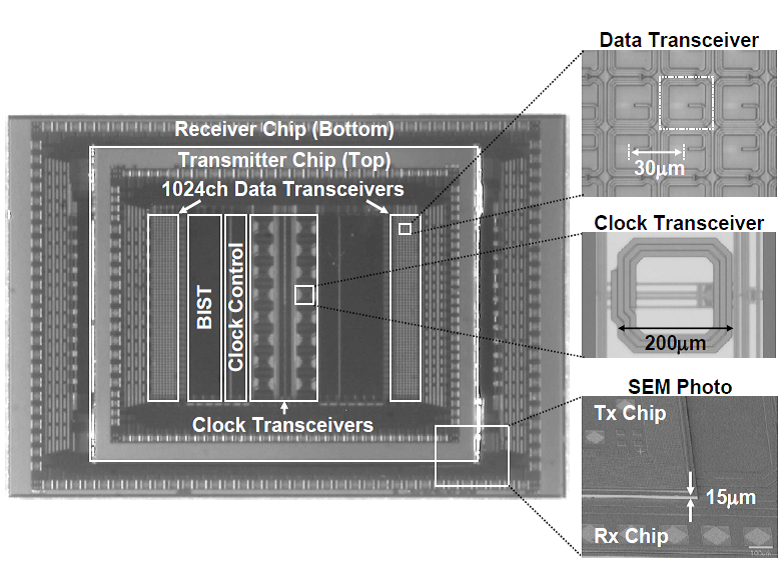

An 8Tb/s 1pJ/b 0.8mm2/Tb/s QDR Inductive-Coupling Interface Between 65nm CMOS GPU and 0.1µm DRAM

PDF 2010

GPU DRAM間のQDR-TCIチャネルを1024チャネル作成しました。ABC回路を用いてPVT ばらつきに対する耐性を向上し、オフセット削減によって消費電力を1pJ/bitまで抑えるこ とに加え、従来手法の1/10以下であるBER<10--16での安定動作を実現しました。

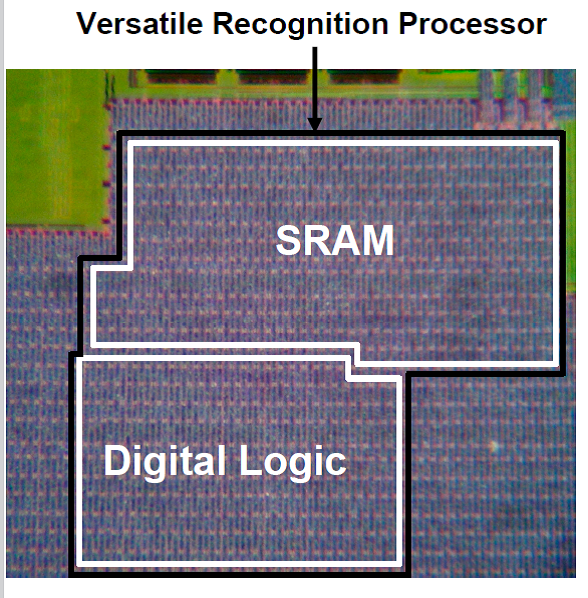

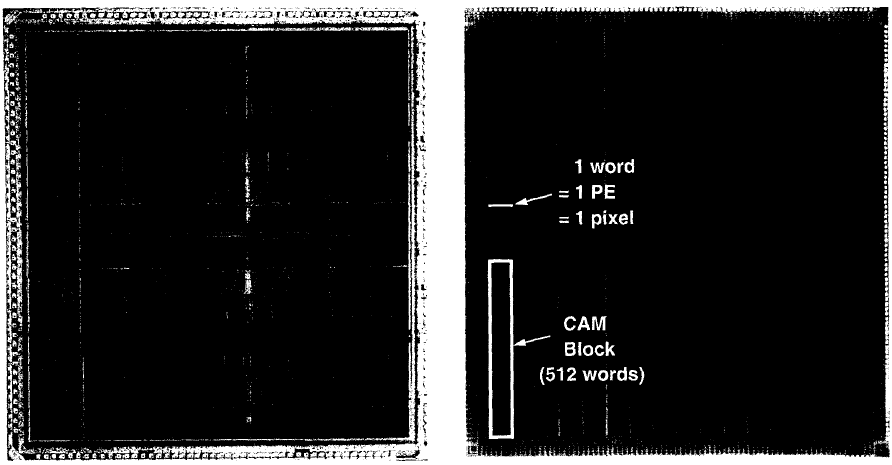

A Versatile Recognition Processor Employing Haar-Like Feature and Cascaded Classifier

PDF 2010

Haar-Like特徴量とカスケードクラス分類を用いた、汎用認識プロセッサを開発しました。エネルギー効率について、0.47mW/fpsを達成し、携帯デバイスやワイヤレスセンサネットワークへの応用が可能です。

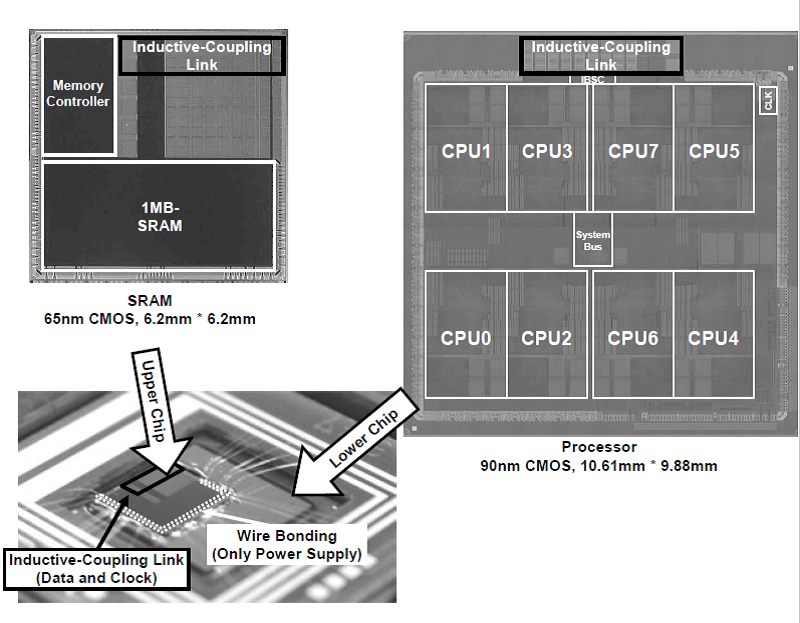

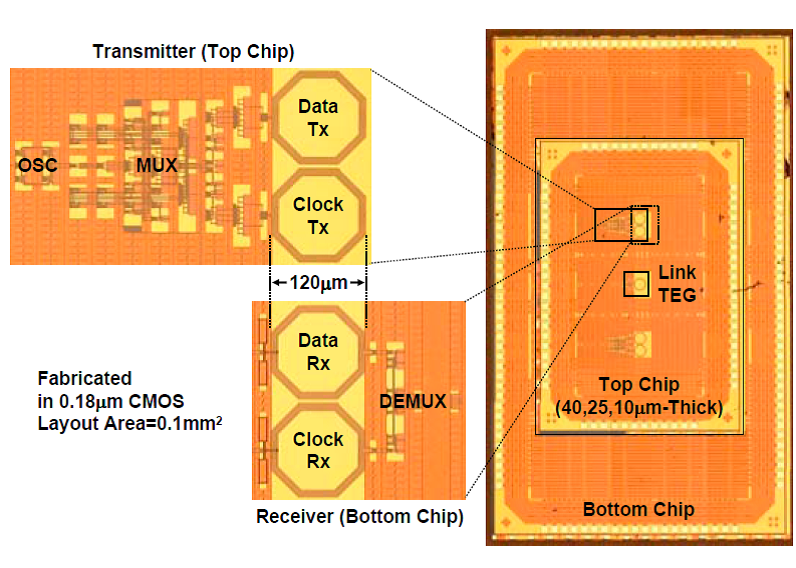

An Inductive-Coupling Link for 3D Integration of a 90nm CMOS Processor and a 65nm CMOS SRAM

PDF 2009

誘導結合を用いて商用プロセッサとメモリを3次元集積したシステムを開発しました。誘導結合通信について、19.2Gb/sの通信速度と、従来の1/30となる1pJ/bのエネルギー効率、1/3となる0.15mm2/Gbpsの面積効率を達成しました。

A 2Gb/s 15pJ/b/chip Inductive-Coupling Programmable Bus for NAND Flash Memory Stacking

PDF 2009

NANDフラッシュメモリの3次元集積のための、誘導結合を用いたプログラム可能なバスを開発しました。各チップの適切な状態プログラミングによって低電力化を図り、2Gb/sのデータレート、15pJ/b/chipのエネルギー効率を達成しました。

Wireless DC Voltage Transmission Using Inductive-Coupling Channelfor Highly-Parallel Wafer-Level Testing

PDF 2009

誘導結合を用いた、多数並列型のウエハレベルテストのための、アナログ直流信号伝送が可能な送受信機を開発しました。この技術により、フラッシュメモリなどのテストを低コストで行うことが可能となります。

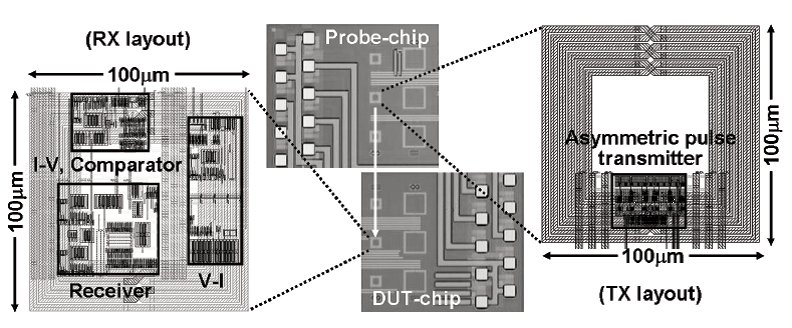

An 11Gb/s Inductive-Coupling Link with Burst Transmission

PDF 2008

チップ間通信において、誘導結合通信は、容量結合通信よりも長い通信距離を確保可能ですが、そのデータレートは1Gb/sと不十分でした。そこで、誘導結合通信に対して非同期送受信機およびバースト送信技術を適用し、11Gb/sを達成しました。

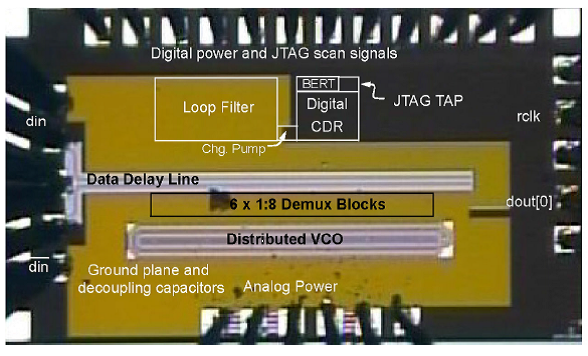

A 40-to-44Gb/s 3× Oversampling CMOS CDR/1:16 DEMUX

PDF 2007

1:16のデマルチプレクサと、BERテスタを備えた、40-40Gb/sのCDRを開発しました。CDRループが低周波のジッタをトラッキングし、3倍のオーバーサンプリングとデジタルCMOSバックエンドが高周波のジッタをトラッキングします。

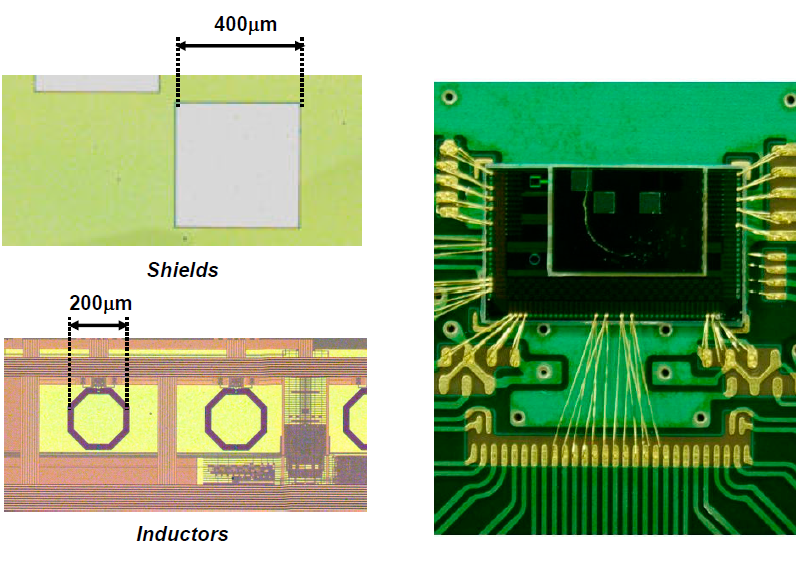

A 0.14pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitally-Controlled Precise Pulse Shaping

PDF 2007

チップ間誘導結合通信は、高速・省電力指向のSiPアプリケーションに対しては、エネルギー効率が不十分でした。そこで、デジタル制御の正確なパルス形成技術を適用することでエネルギー効率改善を図り、0.14pJ/bを達成しました。

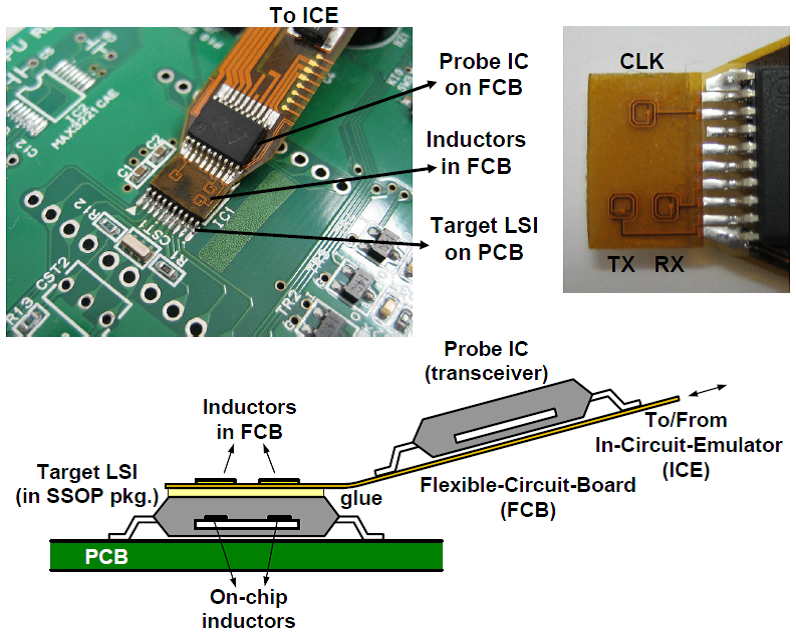

An Attachable Wireless Chip Access Interface for Arbitrary Data Rate Using Pulse-Based Inductive-Coupling through LSI Package

PDF 2007

誘導結合を用いた、取付可能な無線インターフェースを開発しました。20Mb/sのデータレート、1.2mmの通信距離を達成し、パッケージ間の通信や、非接触高速メモリアクセスなど、様々なアプリケーョンに応用可能です。

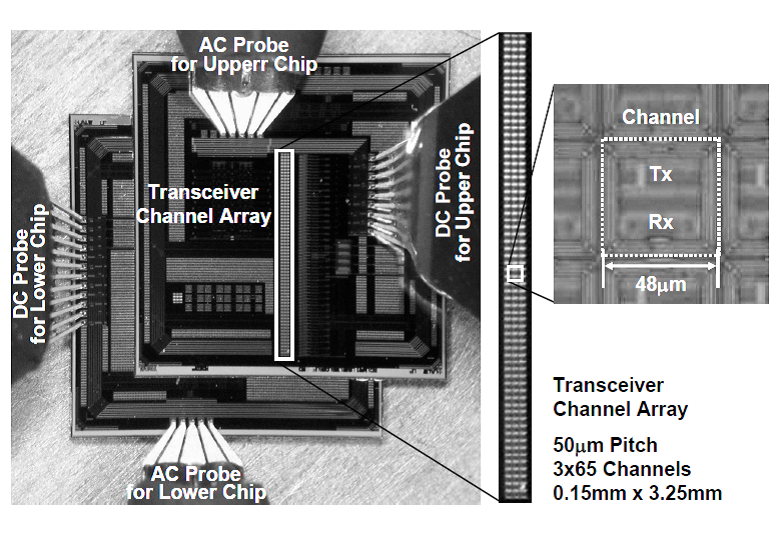

A 1Tb/s 3W Inductive-Coupling Transceiver for Inter-Chip Clock and Data Link

PDF 2006

従来に比べて最高の性能となる、1Tb/s、3Wのチップ間誘導結合通信システムを開発しました。TDMA方式の適用により、クロストークを低減し、2位相偏移変調によってノイズ耐性を向上させ、低電力化を達成しました。

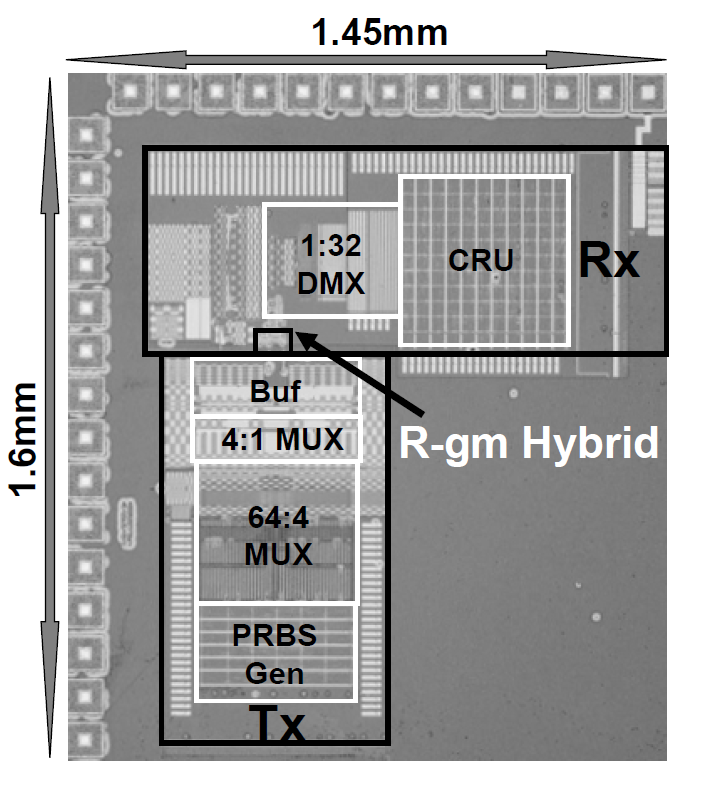

A 20Gb/s Bidirectional Transceiver Using a Resistor-Transconductor Hybrid

PDF 2006

双方向通信は、データレートを向上させる魅力的な技術ですが、従来のレプリカを使う方式では、ミスマッチなどが原因で帯域幅が制限されていました。そこで、抵抗-トランスコンダクタ方式を提案し、20Gb/sを達成しました。

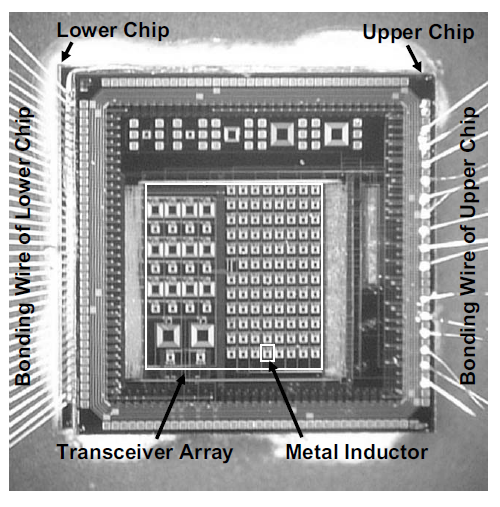

A 195Gb/s 1.2W 3D-Stacked Inductive Inter-Chip Wireless Superconnect with Transmit Power Control Scheme

PDF 2005

送信電力制御機構を用いた、誘導結合によるチップの3次元集積技術を開発しました。通信距離に応じて送信電力を制御することで、電力およびクロストークを削減できます。195Gb/s、1.2Wを達成しました。

A 1.2Gb/s/pin Wireless Superconnect Based on Inductive Inter-Chip Signaling (IIS)

PDF 2004

電圧モード制御の容量結合によるチップ間インターフェースは、プロセススケーリングに伴う低電源電圧化に対応できません。そこで、電流モード制御の誘導結合によるチップ間インターフェースを開発し、1.2Gb/s/pinを達成しました。

1.27Gbps/pin, 3mW/pin Wireless Superconnect (WSC) Interface Scheme

PDF 2003

内部回路の帯域幅に比べ、I/Oの帯域幅は狭く、そのギャップは増大しています。そこで、高密度、高速、低電力のI/Oを実現する技術として、容量結合を用いてチップ間を結合する無線インターフェースを開発し、1.27Gbps/pin、3mW/pinを達成しました。

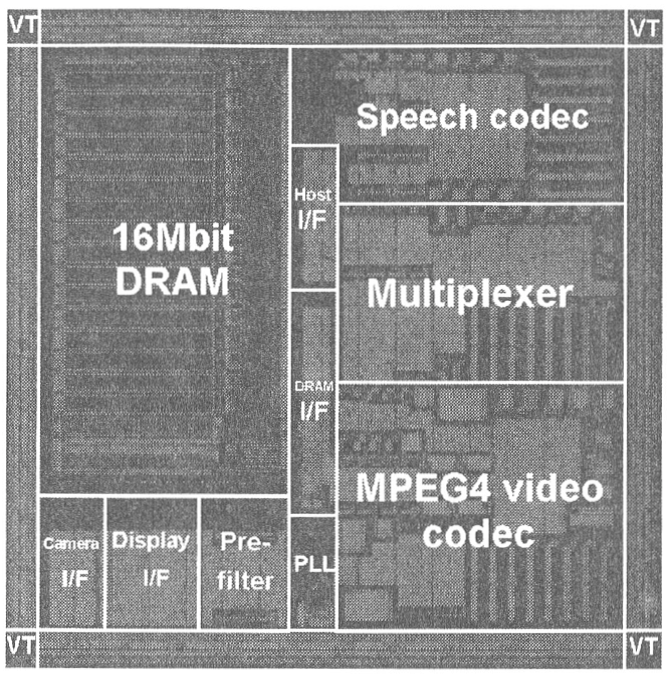

A 60MHz 240mW MPEG-4 Video-Phone LSI with 16Mb Embedded DRAM

PDF 2000

高性能MPEG-4ビデオフォンLSIを開発しました。16MbitのDRAMと、MPEG-4ビデオコーデック、スピーチコーデック、マルチプレクサを搭載しており、60MHzの動作速度で、従来の22%となる240mWの消費電力を達成しました。

Flip-flop Selection Technique for Power-delay Trade-off

PDF 1999

複数種類のフリップフロップを併用して、電力と遅延のトレードオフを取る技術を提案しました。実際にDCTを行うコアについて、高速動作型と低電力型を開発し、前者については25%の速度向上、後者については24%-51%の低電力化を達成しました。

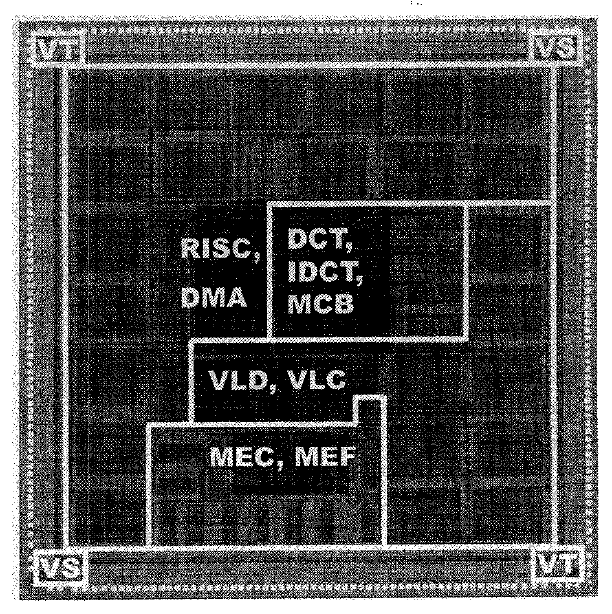

A 60mW MPEG4 Video Codec Using Clustered Voltage Scaling with Variable Supply-Voltage Scheme

PDF 1998

高性能MPEG4ビデオコーデックを開発しました。電源電圧可変調整技術を用いたクラスター化電圧スケーリングによって低電力化を図り、30MHzの動作速度において、従来の30%となる、60mWの消費電力を達成しました。

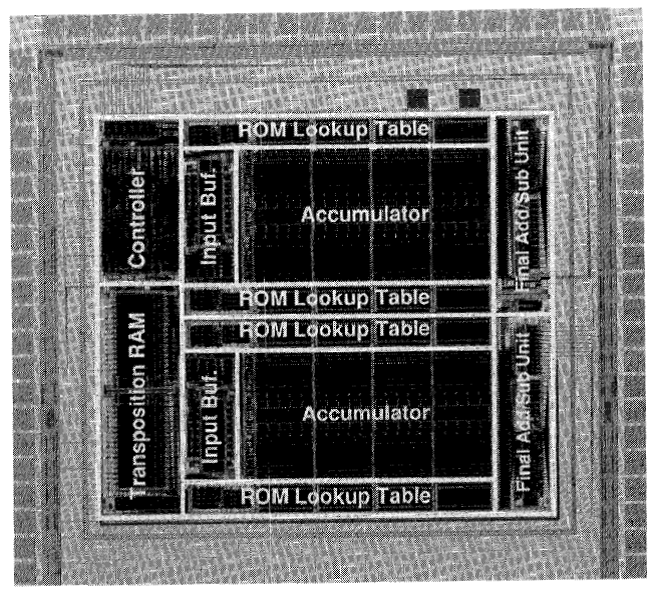

A 0.9V 150MHz 10mW 4mm2 2-D Discrete Cosine Transform Core Processor with Variable-Threshold-Voltage Scheme

PDF 1996

8×8の2次元離散コサイン変換を行うコアプロセッサを開発しました。閾値電圧調整可変技術を用いることで、システムの高速化と低電力化を両立させ、さらにはPVT変動に対する耐性の向上を実現しました。

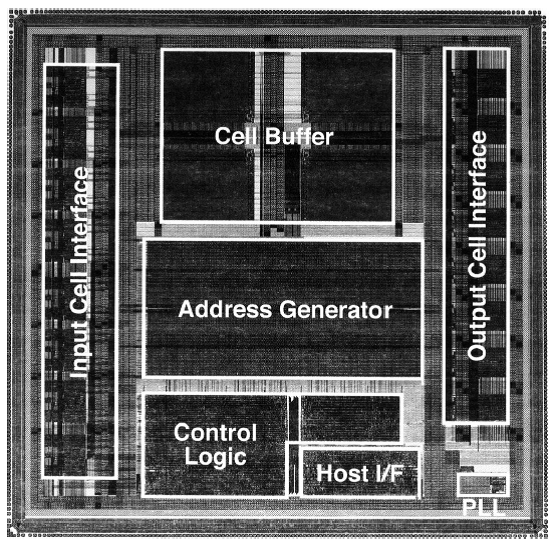

A 5Gb/s 8 x 8 ATM Switch Element CMOS LSI Supporting Five Quality-of-Service Classes with 200MHz LVDS Interface

PDF 1996

LAN/WANアプリケーションのための、200MHzのLVDSインターフェースを用いた、622Mb/s、8×8の共有バッファを搭載する、ATMスイッチLSIを開発しました。5Gbpsの帯域幅をもち、5つのQoSクラスをサポートします。

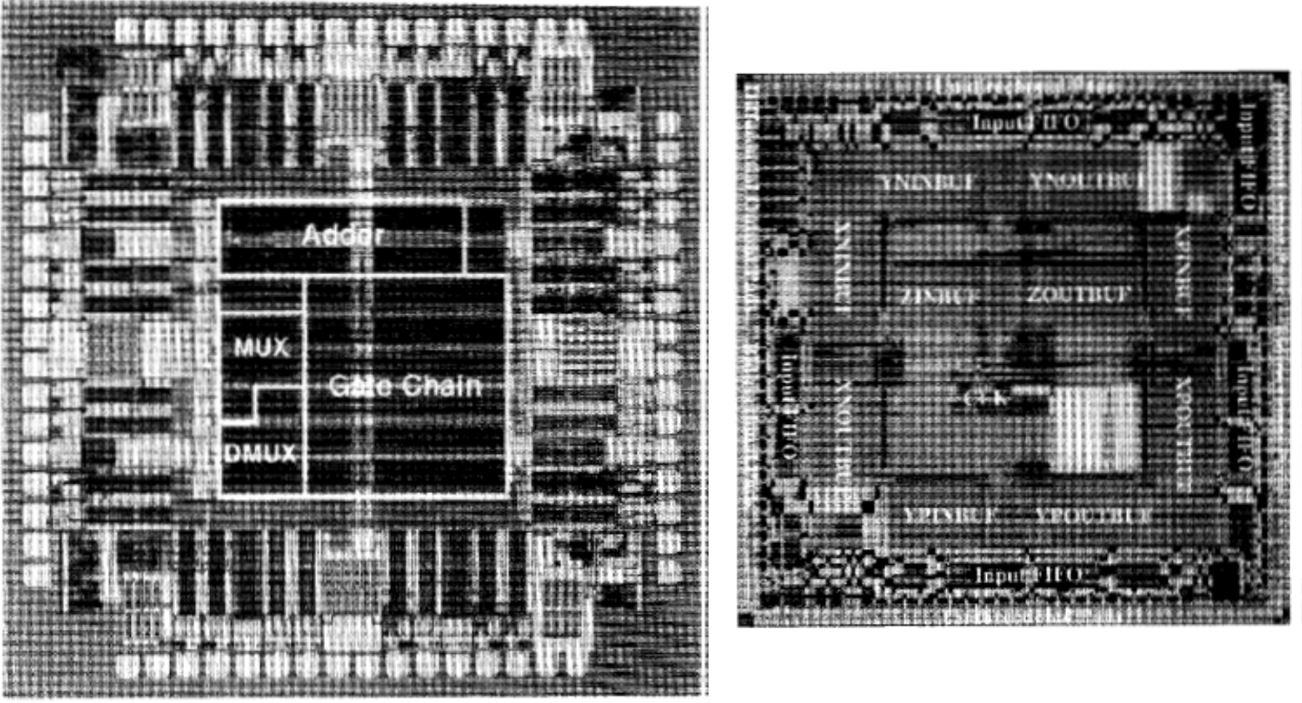

1.65Gb/s 60mW 4:1 Multiplexer and 1.8Gb/s 80mW 1:4 Demultiplexer ICs Using 2V 3-level Series Gating ECL Circuits

PDF 1995

高性能な4:1マルチプレクサおよび1:4デマルチプレクサを開発しました。電源電圧2Vの、3段のシリーズゲートECLを用いることで、マルチプレクサについて1.65Gb/s 60mW、デマルチプレクサについて1.8Gb/s 80mWを達成しました。

50% ActivePower Saving without Speed Degradation using Standby Power Reduction (SPR) Circuit

PDF 1995

LSIの高速・低電力の両立のためには、電源電圧を下げ、低閾値電圧のトランジスタを用いる必要がありますが、リーク電流の増大が課題でした。そこで、基板バイアスを用いてシステム待機時のリーク電流を削減する技術を提案しました。

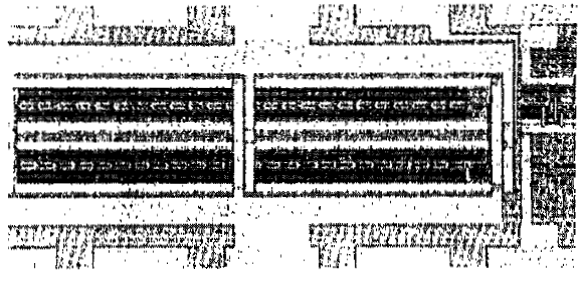

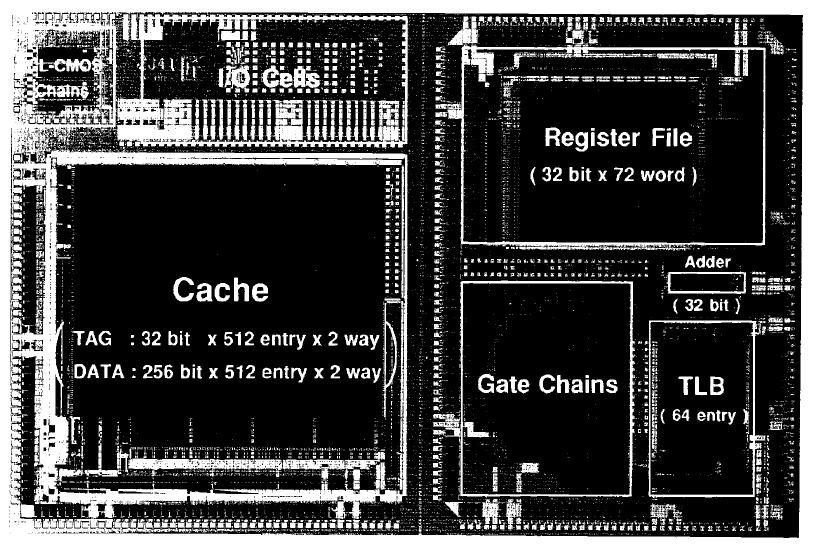

0.5µm BiCMOS Standard-Cell Macros Including 0.5W 3ns Register File and 0.6W 5ns 32kB Cache

PDF 1992

低電力・高速BiCMOSスタンダードセルマクロを開発しました。プロセスは0.5µmのBiCMOSで、100MHzの動作において、0.5W 3nsのレジスタファイル、0.6W 5ns 32KBのキャッシュ、0.2W 2.5nsのTLB、0.1W 3.0nsの加算器を搭載しています。