VLSI Symposium

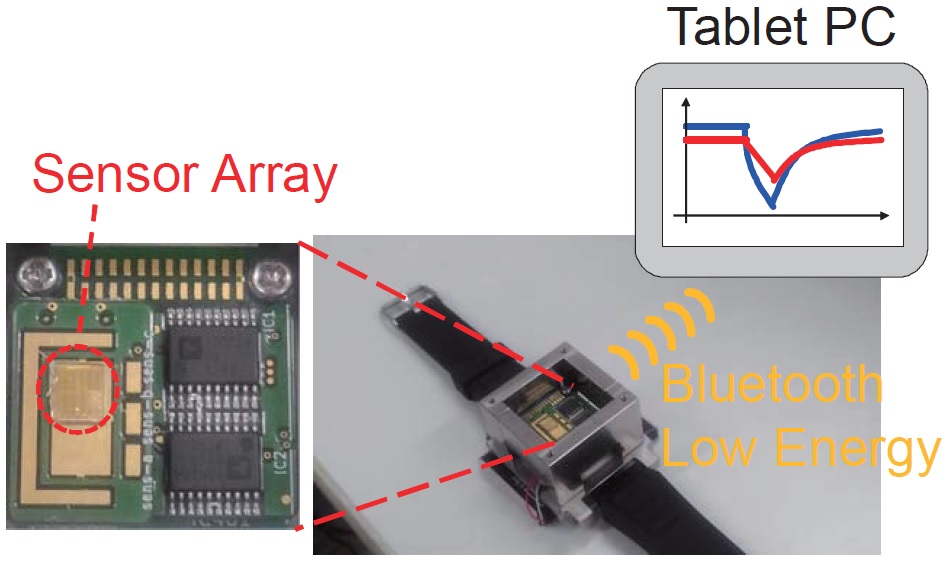

Low-Power and ppm-Level Detection of Gas Molecules by Integrated Metal Nanosheets

PDF 2019

空気中の水素とアンモニアをppm単位で検出する金属触媒ナノシート低電力集積ガスセンサを開発しました。電力を0.14mWまで削減しました。低電力で小面積なため、IoT向けセンサのオンチップ集積が可能になります。センサはプラットホームとの無線接続を達成しました。

Fully integrated OOK-powered pad-less deep sub-wavelength-sized 5-GHz RFID with on-chip antenna using adiabatic logic in 0.18μm CMOS

PDF 2018

オンオフキーイング給電と断熱的論理回路を用いた、完全集積型小型パッシブRFIDタグを開発しました。キャリア波長の約1/30の大きさで、10cmの通信距離を達成しました。バーコードなどに代わり、製品のトレーサビリティの向上に役立ちます。

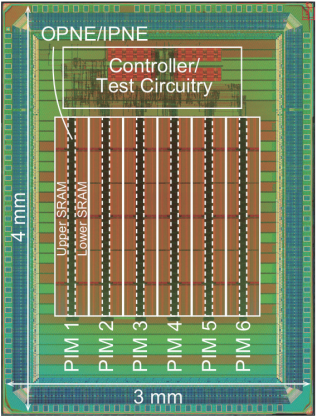

BRein Memory: A 13-Layer 4.2 K Neuron/0.8 M Synapse Binary/Ternary Reconfigurable In-Memory Deep Neural Network Accelerator in 65 nm CMOS

PDF 2017

バイナリー/ターナリ―のディープニューラルネットワークに用いる多目的で再構成可能なアクセラレータを開発しました。0.6 W、1.4 TOPSを実現し、また、CPU、GPU、FPGAに比べ10-104倍の電力効率を実現しました。

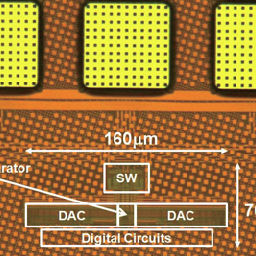

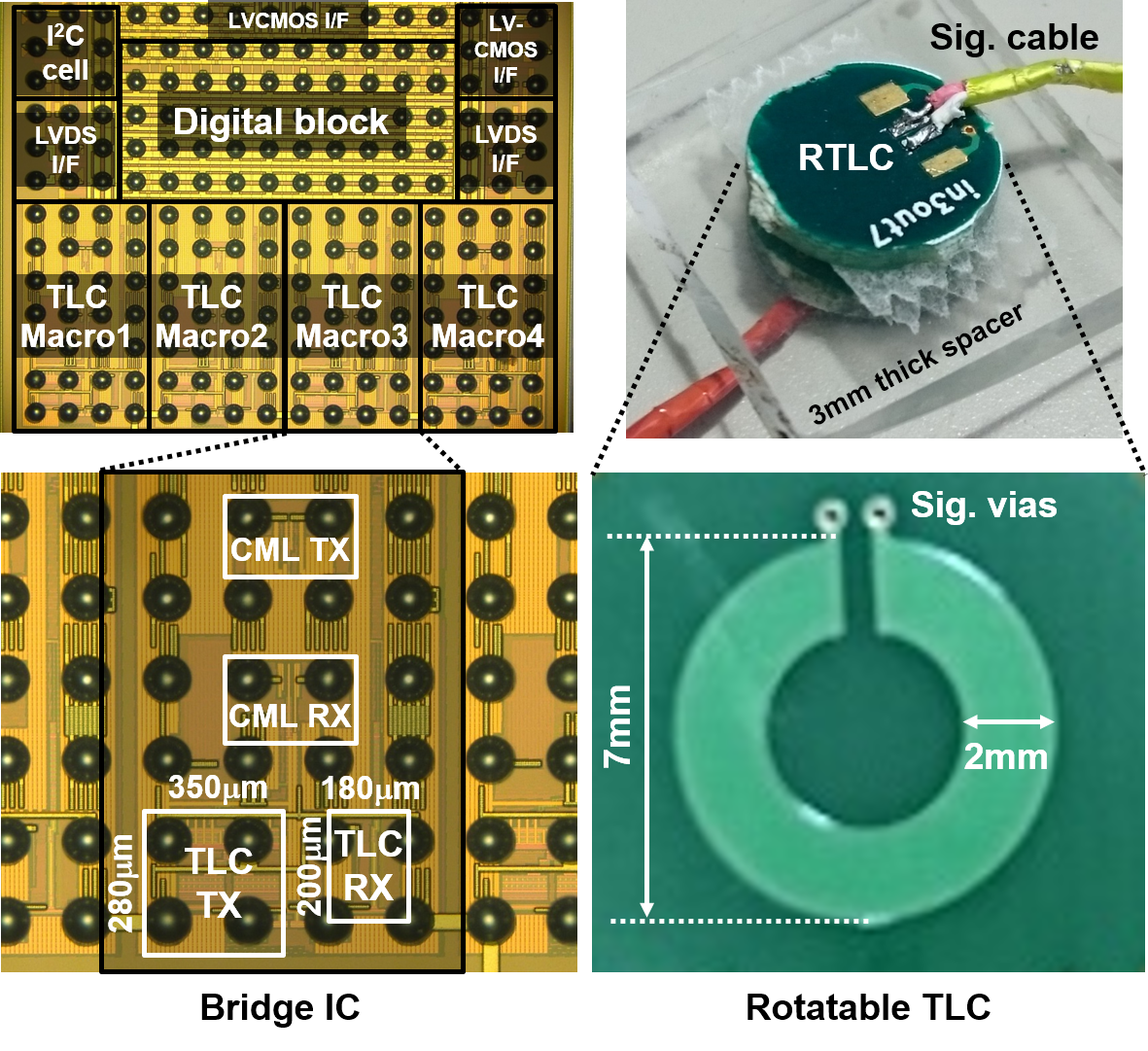

A 6Gb/s Rotatable Non-Contact Connector with High-Speed/I2C/CAN/SPI Interface Bridge IC

PDF 2017

360度回転可能な非接触コネクタとブリッジチップを開発しました。回転しながら6Gbpsの高速通信が可能で、非接触のため摩耗や油などに対する信頼性に優れます。I2CやSPI、CAN等の低速I/Fにも接続可能です。

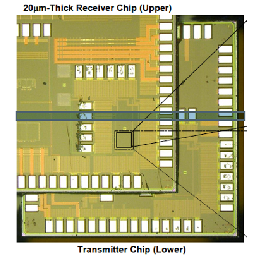

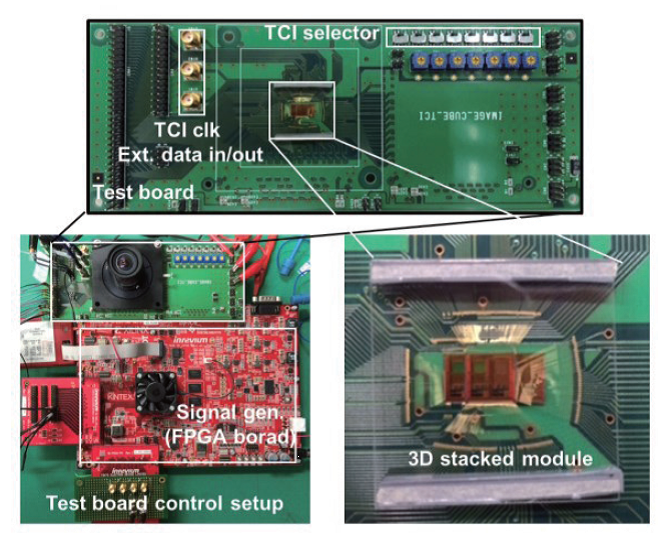

Image Sensor/Digital Logic 3D Stacked Module featuring Inductive Coupling Channels for High Speed/Low-Noise Image Transfer

PDF 2015

高速・低ノイズイメージ伝送のための、誘導結合通信を用いた、イメージセンサとデジタルロジックを3次元集積したモジュールを開発しました。また、間欠動作するTDCを適用したADCを提案し、速い読み出し速度と低消費電力を達成しました。

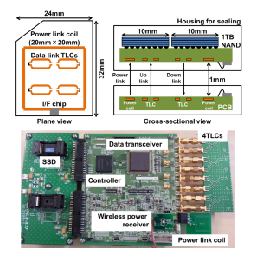

Inductively-Powered Wireless Solid-State Drive (SSD) System with Merged Error Correction of High-Speed on-Contact Data Links and NAND Flash Memory

PDF 2015

無線SSDメモリーカードシステムを開発しました。金属端子が無いため防水・異物・摩耗に強い耐性を持ちます。無線給電とTLCによる無線通信間に干渉は無く、水没させた状態でも正常に動作します。

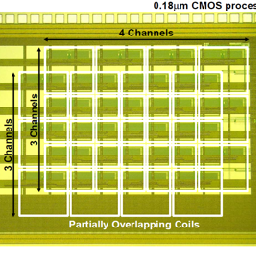

A 352Gb/s Inductive-Coupling DRAM/SoC Interface Using Overlapping Coils with Phase Division Multiplexing and Ultra-Thin Fan-Out Wafer Level Package

PDF 2014

従来TCIと比較して12倍の面積効率向上を達成しました。位相分割多重(PDM)によりコイル密度を増加させ、またウェハの薄膜化により短い通信距離を実現できます。制御する位相の数を増やすことで、今後さらなる通信の高速化が期待されます。

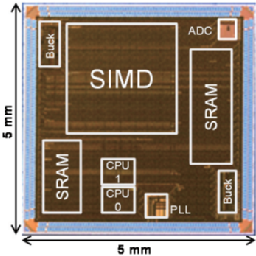

0.5V Image Processor with 563 GOPS/W SIMD and 32bit CPU Using High Voltage Clock Distribution (HVCD) and Adaptive Frequency Scaling (AFS) with 40nm CMOS

PDF 2013

エネルギー効率の高い画像プロセッサを開発しました。タイミング制御に必要となるバッファ回路の数を抑えることで面積効率や回路遅延を低減できます。また、バック・コンバータのリップルの影響を抑えることで33%の高速化を達成しました。

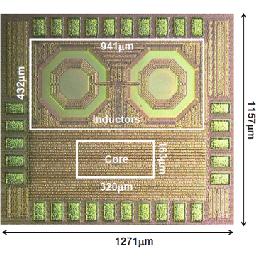

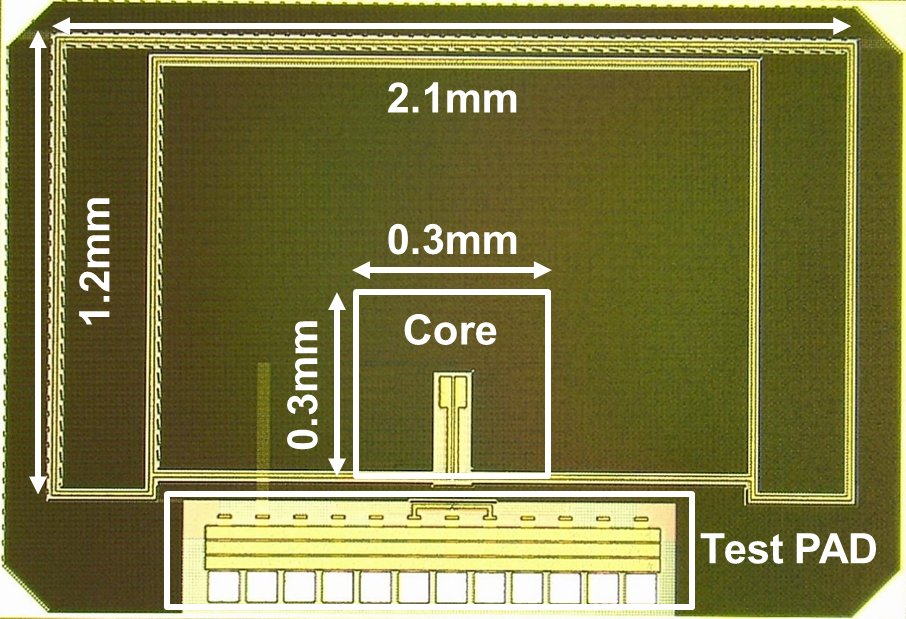

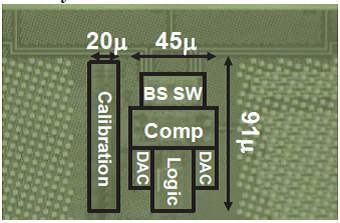

A 0.0058mm2 7.0 ENOB 24MS/s 17fJ/conv. Threshold Configuring SAR ADC with Source Voltage Shifting and Interpolation Technique

PDF 2013

ソース電圧シフト技術と、閾値補償技術を用いた、閾値設定逐次比較型ADCを開発しました。0.0058mm2の面積で、7.0bitの有効ビット数、24MS/sのサンプリングレート、17fJ/conversion-stepのエネルギー効率を達成しました。

A 720μW 873MHz-1.008GHz Injection-Locked Frequency Multiplier with 0.3V Supply Voltage in 90nm CMOS

PDF 2013

低電圧動作可能な周波数逓倍器を開発しました。トランジスタの代わりにバラクタを用いることで、低電圧においてもPVTばらつきへの耐性を確保できます。また発振によって得られる大きな出力振幅は、位相雑音の低減に寄与します。

A 0.5V 1.1MS/sec 6.3fJ/conversion-step SAR-ADC with Tri-Level Comparator in 40nm CMOS

PDF 2011

低電圧動作・高効率の逐次比較型(SAR)ADCを開発しました。コンパレータの速度要求の緩和およびDACの分解能の1bit減少のため、3レベルコンパレータを提案しました。試作ADCは0.5V電源、1.1MS/secでSNDR46.8dBおよびFOM値6.3fJを実現しました。

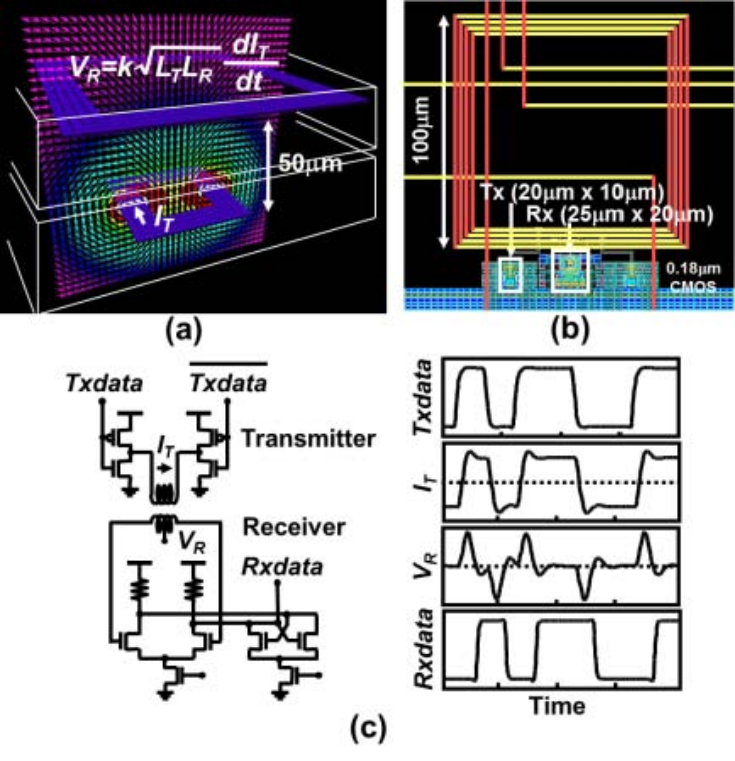

Near-Field Wireless Connection for 3D-System Integration

PDF 2012

誘導結合を用いたチップ間の無線通信技術TCI (ThruChip Interface)を開発しました。TCIは既存のCMOSプロセスで、TSVと並ぶ性能を持ちながら低コストでチップ間の通信を実現します。

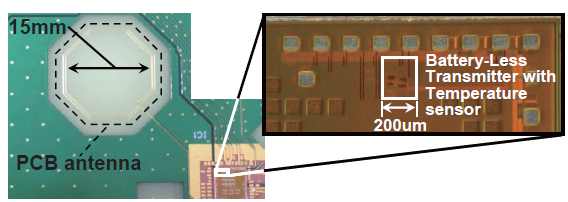

A Battery-less WiFi-BER modulated data transmitter with ambient radio-wave energy harvesting

PDF 2010

ビットエラーレート変調を用いたバッテリーレス送信機を開発しました。250mWの送信電力を持つWiFiアクセスポイントから、30cmの通信距離において、30.8µWの電力を収穫し、5.5kbpsの通信が可能です。

Simultaneous 6Gb/s Data and 10mW Power Transmission using Nested Clover Coils for Non-Contact Memory Card

PDF 2010

同時データおよび誘導結合電力伝送を用いた非接触メモリーカードとホストを開発しました。入れ子のクローバー型データコイルによって干渉を減少させました。試作機は100~2kΩの負荷においてデータレート6Gb/sおよび約10%の電力伝送効率上昇を実現しました。

A 0.7V 20fJ/bit Inductive-Coupling Data Link with Dual-Coil Transmission Scheme

PDF 2010

20fj/bitの誘導結合データリンクおよび135fJ/サイクルのクロックリンク動作を開発しました。デュアルコイル配置によって低電力動作が可能であり、0.7V電源でBER<10-12、データレート1.1Gb/s、クロックレート3.3GHzを実現しました。

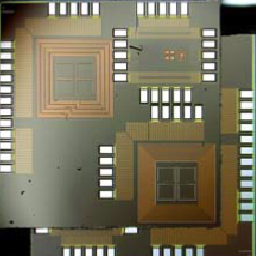

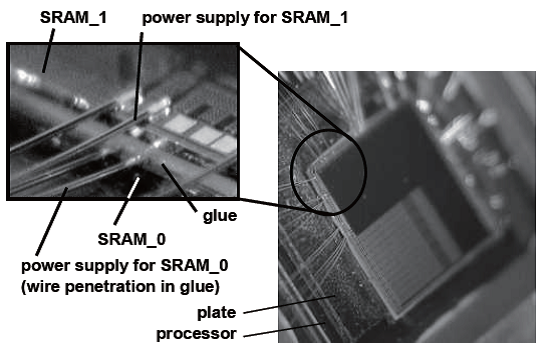

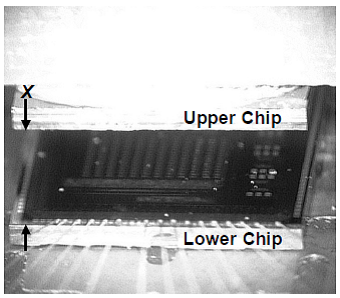

3D System Integration of Processor and Multi-Stacked SRAMs by Using Inductive-Coupling Links

PDF 2009

誘導結合通信を用いた、プロセッサと複数のSRAMのチップを3次元集積したシステムを、世界で初めて実証しました。通信において、1pJ/bのエネルギー効率、0.15mm2/Gbpsの面積効率を達成しました。

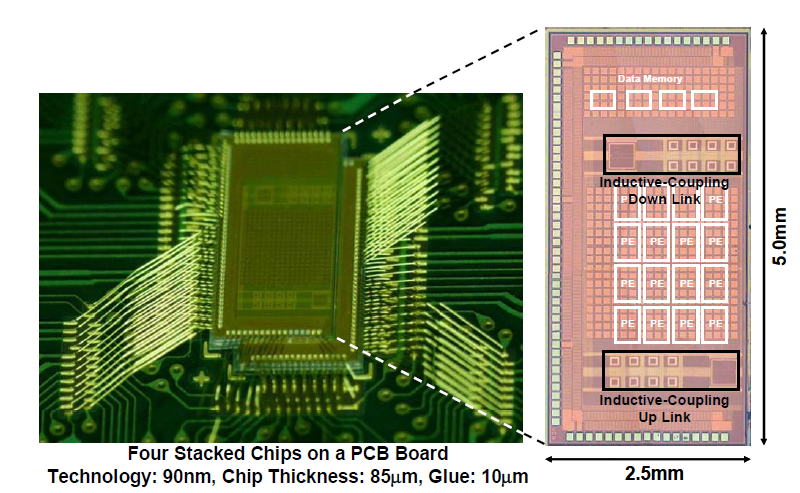

A Scalable 3D Processor by Homogeneous Chip Stacking with Inductive-Coupling Link

PDF 2009

誘導結合通信を用いた、同種チップの3次元集積による、スケーラブル3Dプロセッサを開発しました。チップ集積数によってプロセッサの性能をスケーリング可能で、4つのチップの集積によって実行時間を31%に短縮可能です。

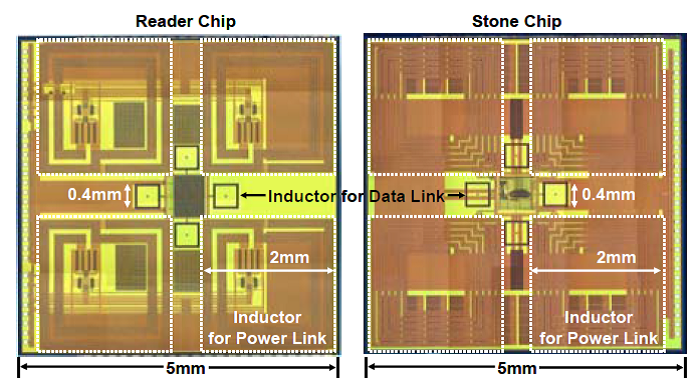

Digital Rosetta Stone: A Sealed Permanent Memory with Inductive-Coupling Power and Data Link

PDF 2009

データの恒久的保存を実現する記憶媒体:デジタルロゼッタストーンを開発しました。デジタルデータをマスクROMに書き込んだウエハを密封して防水し、誘導結合を用いて給電及び通信を非接触で行います。

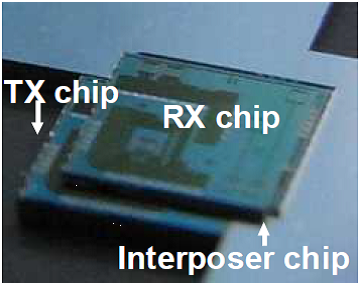

A 4.7Gb/s Inductive Coupling Interposer with Dual Mode Modem

PDF 2009

世界で初めて誘導結合を用いたインターポーザを開発し、データレートについて、4.7Gb/s/chを達成しました。3次元集積システムに対して、容量結合による手法よりも柔軟なチップ設計を提供できます。

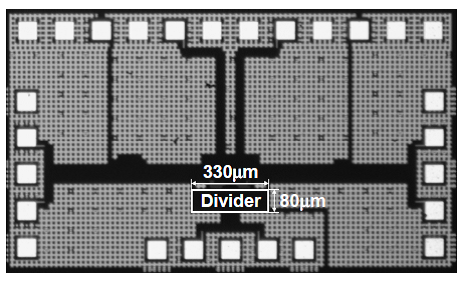

A 20-GHz Injection-Locked LC Divider with a 25-% Locking Range

PDF 2006

注入同期型LC分周器を開発しました。結合回路とともにミラー分周器を用いることで、20GHzにおいて、25%の広いロックレンジを達成しました。これにより、LC-VCOのチューニングレンジを十分にカバー可能です。

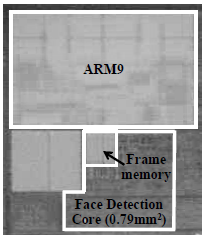

A 0.79mm2 29mW Real-Time Face Detection Core

PDF 2006

リアルタイム顔検出コアを開発しました。アルゴリズムとハードウェアの包括的な最適化により、小面積、低電力を達成しました。30fpsにおいて、1フレーム当たり8つの顔を検出可能です。

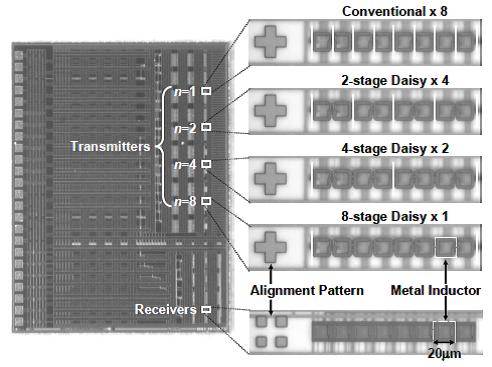

Daisy Chain for Power Reduction in Inductive-Coupling CMOS Link

PDF 2006

誘導結合通信について、電流駆動型送信機に、デイジーチェーンを用いて低電力化を図りました。デイジーチェーンによって電荷を再利用し、データレートとBERを損なうことなく、35%の送信電力削減を達成しました。

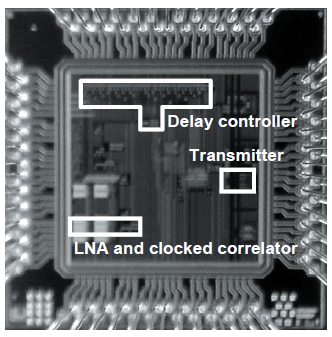

A CMOS Impulse Radio Ultra-Wideband Tranceiver for 1Mb/s Data Communications and ±2.5cm Range Findings

PDF 2005

超広帯域バルス無線機を開発しました。0.7mWの送信機電力、4.0mWの受信機電力で、1Mb/sの通信が可能です。また、0.7µWの送信機電力で、秒間1000回、精度±2.5cmの距離測定が可能です。

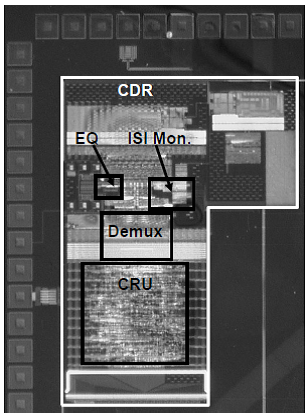

A 10Gb/s Receiver with Equalizer and On-chip ISI Monitor in 0.11µm CMOS

PDF 2004

イコライザ、ISIモニタ、クロックデータリカバリからなる受信機を開発しました。イコライザについて、Cherry-Hooper型増幅回路の応用により高帯域幅、小面積、低電力を実現し、ISIモニタによりイコライザをチューニング可能です。

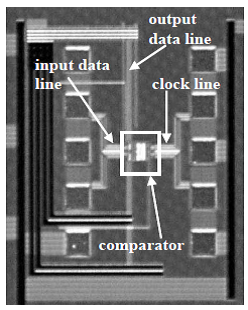

A 0.11µm CMOS Clocked Comparator for High-Speed Serial Communications

PDF 2004

40Gb/sの信号を目標とする、高速シリアル通信用差動クロックドコンパレータを開発しました。8GHzのトリガーレートにおいて、32Gb/sの差動信号をサンプリング可能であることを確認しました。

Analysis and Design of Transceiver Circuit and Inductor Layout for Inductive Inter-chip Wireless Superconnect

PDF 2004

チップ積層のための誘導結合通信について、インダクタのレイアウト最適化手法および送受信回路の設計法について提案しました。作成した理論解析モデルについて、その正確性をテストチップにより確かめました。

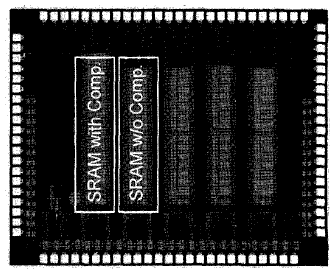

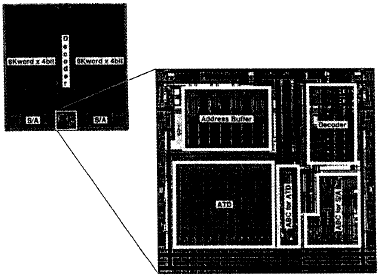

A Bit-Line Leakage Compensation Scheme for Low-Voltage SRAM's

PDF 2000

低電圧SRAMの、ビットラインリーク電流に対する補償技術を提案しました。この技術により、SRAMにおいてトランジスタの閾値電圧を低くすることが可能で、動作速度を25%向上させます。

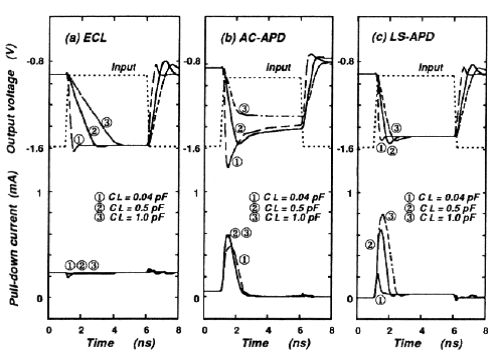

Capacitor-free level-sensitive active pull-down ECL circuit with self-adjusting driving capability

PDF 1993

エミッタ結合論理用自己調整アクティブプルダウン回路を提案しました。アプリケーションによっては、3.5倍の動作速度、または7.1倍の省電力性を実現できます。また、参照電圧生成用の電圧制限回路も提案しました。

Automated Bias Control (ABC) Circuit for High-Performance VLSIs

PDF 1991

BiCMOSテクノロジー用自動バイアス制御回路を開発しました。動作マージンとプロセスばらつきへの耐性を向上させ、VLSIの高性能化に繋がります。センスアンプなどのアプリケーションに応用可能です。